# **SEL-287V SEL-187V**

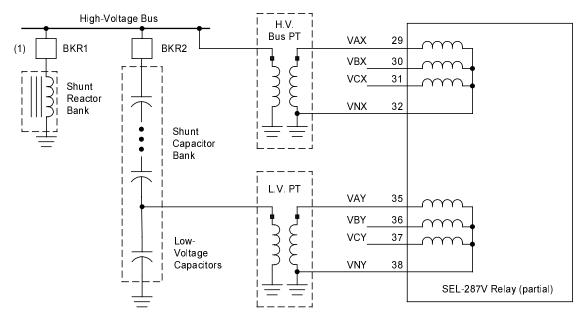

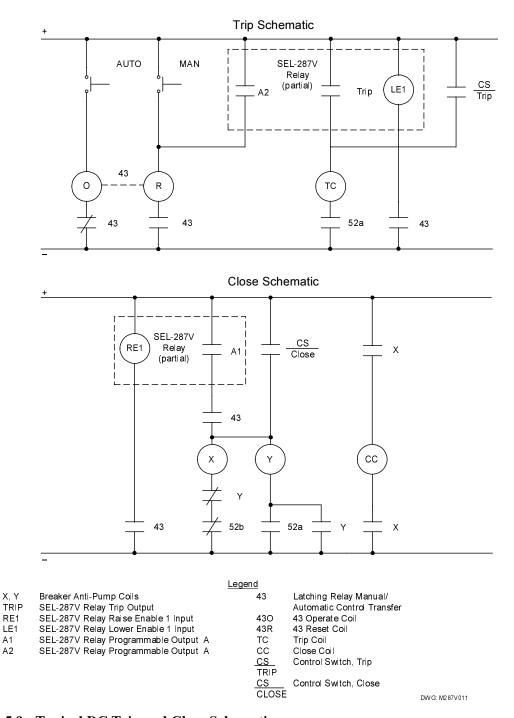

# VOLTAGE LEVEL RELAY VOLTAGE DIFFERENTIAL RELAY VOLTAGE CONTROLLER

### **INSTRUCTION MANUAL**

SCHWEITZER ENGINEERING LABORATORIES 2350 NE HOPKINS COURT PULLMAN, WA USA 99163-5603 TEL: (509) 332-7990 FAX: (509) 332-7990

The software (firmware), schematic drawings, relay commands, and relay messages are copyright protected by the United States Copyright Law and International Treaty provisions. All rights are reserved.

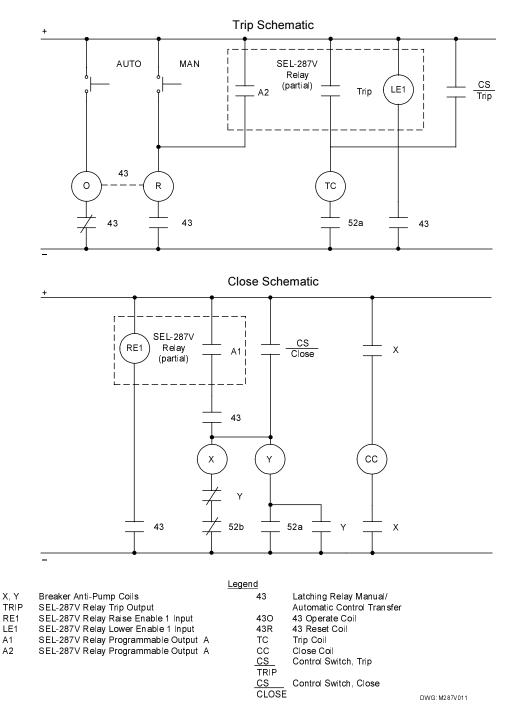

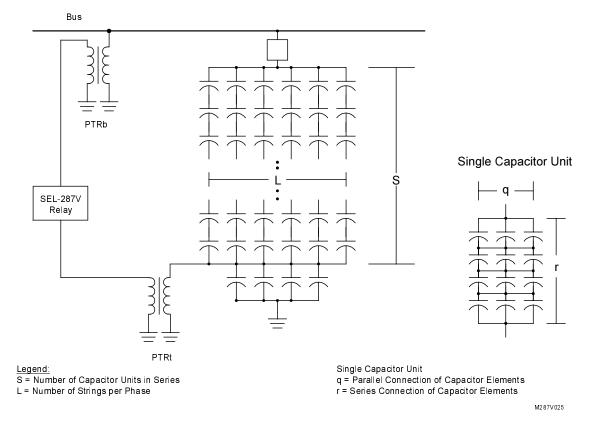

You may not copy, alter, disassemble, or reverse-engineer the software. You may not provide the software to any third party.

All brand or product names appearing in this document are the trademark or registered trademark of their respective holders.

Schweitzer Engineering Laboratories, SELOGIC, Connectorized, Job Done, SELPROFILE, and SEL are registered trademarks of Schweitzer Engineering Laboratories.

The English language manual is the only approved SEL manual.

$Copyright © SEL \ 1990, 1991, 1992, 1996, 1997, 1999, 2000, 2001 \ (All \ rights \ reserved) \ Printed \ in \ USA.$

This product is covered by U.S. Patent No: 5,479,315.

This product is covered by the standard SEL 10-year warranty. For warranty details, visit www.selinc.com or contact your customer sales representative.

#### MANUAL CHANGE INFORMATION

The date code at the bottom of each page of this manual reflects the creation or revision date. Date codes are changed only on pages that have been revised and any following pages affected by the revisions (i.e., pagination). If significant revisions are made to a section, the date code on all pages of the section will be changed to reflect the revision date.

Each time revisions are made, both the main table of contents and the affected individual section table of contents are regenerated and the date code is changed to reflect the revision date.

Changes in this manual to date are summarized below (most recent revisions listed at top).

| Revision<br>Date | Summary of Revisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  | <b>Change Information</b> section has been created to begin a record of revisions to All changes will be recorded in this Summary of Revisions table.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

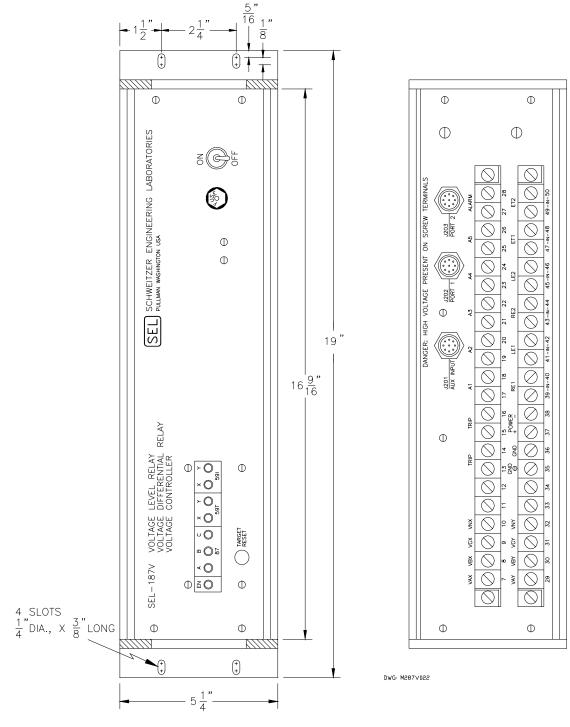

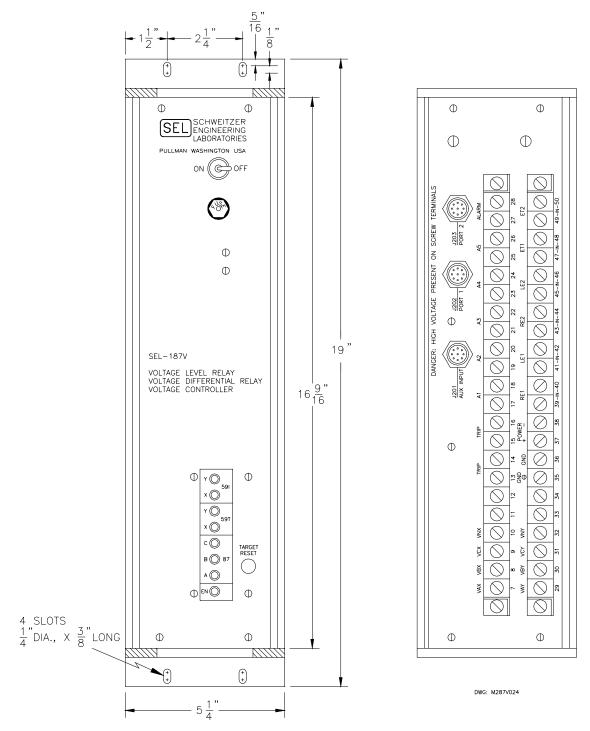

| 20011116         | Made typographical correction in <i>Section 1: Introduction</i> ; added Terminal Connections specification, deleted Shipping Weight specification, and corrected specifications for Voltage Elements and Voltage Differential Elements in <i>Section 2: Specifications</i> ; added explanatory tables for the Externally/Fused Grounded-Wye Capacitor Bank Example in <i>Section 5: Applications</i> ; corrected targets and inputs and included updated relay dimension drawing in <i>Section 6: Installation</i> ; updated Factory Assistance paragraph in <i>Section 7: Maintenance and Testing</i> . |  |  |  |

| 20010223         | Figure 2.1 in Section 2: Specifications corrected replacing an OR gate with an AND gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 20000918         | Manual reissued; added application information to Section 5: Applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 990312           | Instruction manual was updated to document the new setting range of the RINGS setting and the added functionality of preventing the relay from writing the new year to EEPROM at midnight New Year's Eve.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                  | <ul> <li>Documented new RINGS setting range and associated new functionality under the SET command in the Section 3: Communications and Appendix C: SEL-287V-2 Relay Information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  | <ul> <li>Updated Settings Sheets in Section 5: Applications and Appendix C:<br/>SEL-287V-2 Relay Information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                  | <ul> <li>Updated <i>Appendix A: Firmware Versions</i> with the revision numbers that include these modifications.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Revision<br>Date | Summary of Revisions                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 970820           | Instruction manual was changed to include material on new SEL-287V-2 versi with special two-zone differential logic. Manual material on SEL-287V/287V versions was updated/corrected in some cases. |  |  |  |  |  |  |

|                  | Manual changes:                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | (1) Added brief description of new version in <i>Introduction</i> .                                                                                                                                 |  |  |  |  |  |  |

|                  | (2) Noted items specific to 287V/287V-1 versions and referred to corresponding 287V-2 items in Appendix C.                                                                                          |  |  |  |  |  |  |

|                  | (3) Added new Appendix C to include all specific information on SEL-287V-2 version.                                                                                                                 |  |  |  |  |  |  |

|                  | (4) Updated drawing in Figure 2.3 and related logic expressions in <i>Intermediate Logic</i> , <i>Differential Overvoltage Conditions</i> , both of which apply to the SEL-287V/287V-1 versions.    |  |  |  |  |  |  |

# SEL-287V/187V INSTRUCTION MANUAL TABLE OF CONTENTS

**SECTION 1: INTRODUCTION**

**SECTION 2: SPECIFICATIONS**

**SECTION 3: COMMUNICATIONS**

**SECTION 4: EVENT REPORTING**

**SECTION 5: APPLICATIONS**

**SECTION 6: INSTALLATION**

**SECTION 7: MAINTENANCE AND TESTING**

**SECTION 8: APPENDICES**

**Appendix A: Firmware Versions**

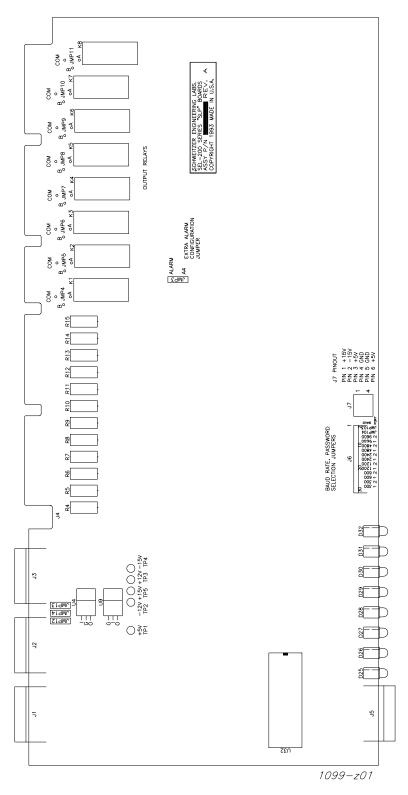

**Appendix B: Internal Diagram**

**Appendix C: SEL-187V Relay Information**

Appendix D: Onebus: Program to Compute Test Set Settings for

**Testing Distance Relays**

## **TABLE OF CONTENTS**

| SECTION 1:    | INTRODUCTION                                   | 1-1 |

|---------------|------------------------------------------------|-----|

| Getting Start | ed                                             | 1-1 |

| Overview      |                                                | 1-1 |

| Model Optio   | ns                                             | 1-2 |

| SEL-18        | 7V Relay                                       | 1-2 |

| SEL-28        | 7V Relay                                       | 1-2 |

| SEL-28'       | 7V-1 Relay                                     | 1-2 |

| SEL-28'       | 7V-2 Relay                                     | 1-2 |

| Phase R       | otation                                        | 1-3 |

| System        | Frequency                                      | 1-3 |

| Application 1 | Ideas                                          | 1-3 |

| Control       | and Protect Grounded-Wye Shunt Capacitor Banks | 1-3 |

| Control       | Two Devices With One Relay                     | 1-3 |

|               | One Device With Two Independent Schemes        |     |

|               | hase Undervoltage Load Shedding                |     |

#### **SECTION 1: INTRODUCTION**

#### **GETTING STARTED**

This instruction manual applies to the SEL-187V and SEL-287V family of relays. The SEL-287V Relay and the SEL-187V Relay have identical protection features, but use different hardware designs. See *Appendix C: SEL-187V Relay Information* for SEL-187V Relay details.

If you are unfamiliar with these relays, we suggest that you read this introduction, then perform the *Initial Checkout* procedure in *Section 7: Maintenance and Testing*. For a more detailed understanding of the relay, we suggest that you read the following sections in the outlined order:

**Section 2: Specifications** for a detailed description of the logic and how it works with logic inputs, the Relay Word, and relay outputs.

**Section 5: Applications** for a description of capacitor banks, an application outline that guides settings selection, and Settings Sheets.

**Section 3: Communications** for a description of the commands used to set the relay for protection, set the relay for control, obtain target information, obtain metering information, etc.

**Section 4:** Event Reporting for a description of event report generation, summary event reports, long event reports, and their interpretation.

#### **OVERVIEW**

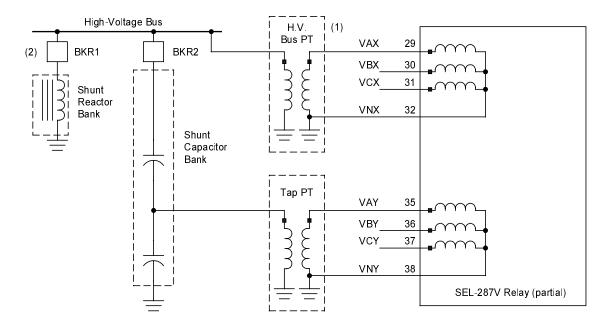

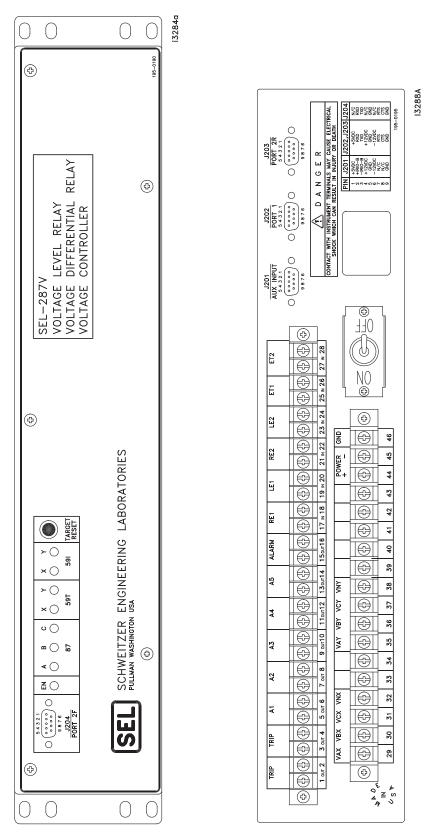

The SEL-287V Relay provides voltage level relay, voltage differential relay, and voltage controller functionality intended to control and protect grounded-wye shunt capacitor banks.

The relay includes event reporting, local and remote setting via two EIA-232 ports, metering, automatic self-testing, and programmable logic masks.

Programmable logic and numerous voltage elements make the relay suitable for many other voltage control and monitoring purposes.

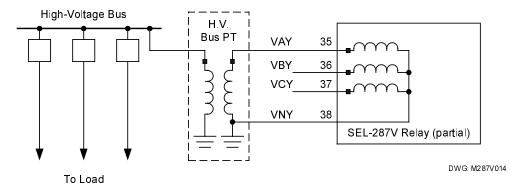

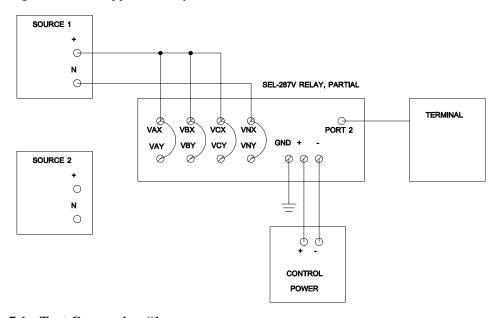

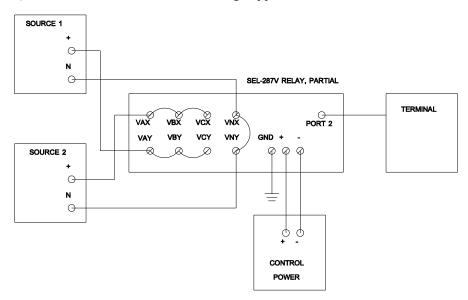

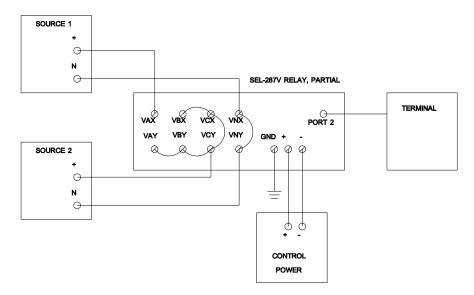

The SEL-287V Relay accepts voltage inputs from two separate three-phase, four-wire sources of potential, referred to as Source X and Source Y.

For each Source X and Y, the relay provides the following:

- Three single-phase overvoltage elements

- Three single-phase undervoltage elements

- One definite-time overvoltage element that responds to maximum phase voltage

- One three-phase overvoltage element intended for voltage control

- One three-phase undervoltage element intended for voltage control

- Voltage control instability detection logic

- Logic inputs to supervise the voltage control scheme

- Automatic scheme which selects preferred source for voltage control

- Four voltage control timers

- Loss-of-potential logic with timer

The SEL-287V Relay features magnitude-voltage-differential protection:

- Three differential elements per phase (six per phase in SEL-287V-2 Relay—alarm, trip, high-set trip;  $dV \le 0$  and dV > 0)

- Separate thresholds for each element

- Adjustable pickup/dropout timers

- Separate ratio adjustment constants for each element and phase

- Loss-of-potential supervision with adjustable timers

General features of the SEL-287V Relay include:

- Eleven-cycle event report

- Twelve latest events stored in history buffer

- Programmable Logic Masks

- Two EIA-232 serial communications ports for setting and reporting

- Metering of all six inputs and the magnitude differences for each phase

- Full automatic self-testing to enhance reliability and availability

#### **MODEL OPTIONS**

#### SEL-187V Relay

This manual is written for the SEL-287V Relay. For SEL-187V Relays, substitute SEL-187V Relay for each reference to the SEL-287V Relay. See *Appendix C: SEL-187V Relay Information* for more details on the SEL-187V Relay.

#### **SEL-287V Relay**

The preceding Overview outlines all the features contained in the basic SEL-287V Relay.

#### SEL-287V-1 Relay

The SEL-287V-1 Relay has modified elements to provide faster pickup and dropout response. This change slightly reduces the element accuracy. Otherwise, this relay is functionally identical to the SEL-287V Relay design. The SEL-287V-1 Relay voltage and differential element accuracy is  $\pm 0.60$  V at 25°C.

#### SEL-287V-2 Relay

The SEL-287V-2 Relay differs from the standard SEL-287V Relay in the 87 voltage differential element logic, used for grounded capacitor bank protection. Separately adjustable voltage threshold settings are added for detection of unbalances above and below the tap point for alarm and trip purposes. The sign of the dVA, dVB, and dVC quantities is used to decide which threshold to apply. Independent A-phase, B-phase, and C-phase alarm thresholds have been eliminated.

In the standard SEL-287V Relay, for example, the A-phase difference voltage is calculated as  $|dVA| = ||VAX| - KA \cdot |VAY||$ , and only this magnitude of dVA is used in the comparison logic. In the SEL-287V-2 Relay, the formula is  $dVA = |VAX| - KA \cdot |VAY|$ , with the sign of dVA retained. If the value of dVA is greater than zero (positive sign), one set of thresholds is used for

the alarm, trip, and high-set trip functions. If dVA is less than zero (negative sign), another set of thresholds is used. The case dVA = 0 is considered a "negative" value. For detection of a blown fuse or fuses in a series group, a positive dVA occurs if the fuse blowing is above the tap, and a negative dVA occurs for fuse blowing below the tap. If the high-set trip unit is applied for detection and high-speed tripping when a series group flashover occurs, a positive dVA represents a flashover below the tap and a negative dVA represents a flashover above the tap, just the opposite of the signs for fuse blowings.

#### **Phase Rotation**

This manual is written for standard ABC phase rotation applications. If you order your SEL relay with the ACB phase option, note references in the instruction manual to voltage and current phase angle accordingly. The firmware identification number (FID) may be used to verify whether your relay was ordered with ABC ("B") or ACB ("C") rotation.

All voltage inputs are connected to the SEL relay rear panel as shown in this instruction manual.

#### **System Frequency**

This manual is written for relays operating at a nominal system frequency of 60 Hz. For relays that specify a nominal frequency of 50 Hz, substitute 50 Hz for each reference to 60 Hz. Replace references to a sampling time of 1/240 second with a time of 1/200 second.

#### **APPLICATION IDEAS**

#### **Control and Protect Grounded-Wye Shunt Capacitor Banks**

The SEL-287V Relay has instantaneous and definite-time overvoltage elements in addition to voltage-magnitude-differential elements. This combination of elements provides complete voltage-based protection for grounded-wye shunt capacitor banks.

The relay voltage differential elements are sensitive, stable, and precise. In most applications the relay can alarm for a single capacitor fuse operation. The KSET command automatically nulls the voltage differences. Mask-programmable event report triggering tailors relay event report generation to your specific requirements.

#### **Control Two Devices With One Relay**

Two separate voltage control schemes perform voltage-based control of two devices, such as a capacitor bank and a reactor bank.

Independently settable voltage control timers help you coordinate voltage control with other system conditions.

The relay loss-of-potential (LOP) logic prevents voltage control operations in the event of blown bus potential transformer fuses.

#### **Control One Device With Two Independent Schemes**

The two separate voltage control logic schemes can be applied to a single device. For example, you can use a long time delay for small variations in system voltage and a shorter time delay for large voltage excursions.

The two schemes are supervised by optoisolator contact inputs. Enable and disable the schemes by asserting the inputs remotely via SCADA or locally via control switch. You can operate both schemes together or each scheme individually. Thus, you can make your voltage control scheme adapt to system configuration and operating conditions.

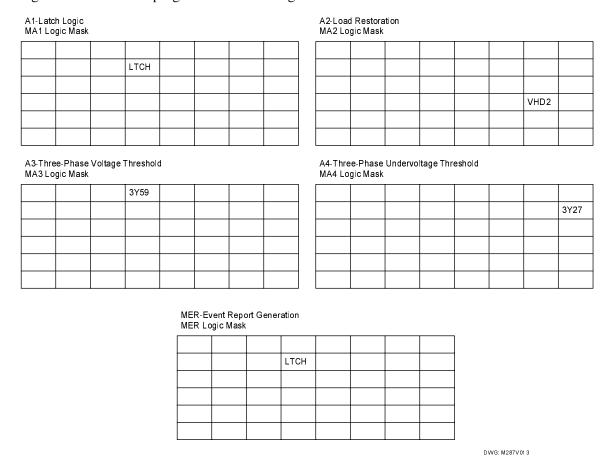

#### **Three-Phase Undervoltage Load Shedding**

The SEL-287V Relay can be used to detect three-phase undervoltage conditions and trip off load (after a settable time delay).

A latching bit in the Relay Word provides a remote (SCADA) or local alarm when the scheme operates. The latch bit can also be used with internal logic to restore load automatically when system voltage conditions return to normal.

## **TABLE OF CONTENTS**

| ECTION 2: SPECIFICATIONS                                 | 2-1  |

|----------------------------------------------------------|------|

| General Specifications                                   | 2-1  |

| Relay Voltage Elements                                   | 2-2  |

| Relay Voltage Differential Elements                      | 2-2  |

| Logic Inputs                                             | 2-3  |

| Relay Outputs                                            | 2-3  |

| TRIP Output                                              |      |

| Programmable Outputs (A1, A2, A3, A4, A5)                | 2-3  |

| ALARM Output                                             | 2-3  |

| Relay Word                                               |      |

| Programmable Logic Masks                                 | 2-6  |

| Output Logic                                             | 2-7  |

| Relay Targets                                            | 2-7  |

| Serial Interfaces                                        | 2-7  |

| IRIG-B Input Description                                 | 2-8  |

| Signal Processing                                        | 2-8  |

| Logic Description                                        | 2-9  |

| Overvoltage/Undervoltage Logic                           | 2-9  |

| Loss-of-Potential Logic                                  |      |

| Definite-Time Overvoltage Logic                          | 2-11 |

| Voltage Differential Logic (SEL-287V, SEL-287V-1 Relays) | 2-11 |

| Voltage Differential Logic (SEL-287V-2 Relays)           |      |

| Differential Overvoltage Conditions                      |      |

| Voltage Control Logic                                    | 2-14 |

| Voltage Selection Scheme                                 |      |

| Voltage Control Instability Logic                        |      |

| Latching Bit Logic                                       |      |

| A1 Through A5 Output Contact Time-Delay Logic            |      |

| Intermediate Logic                                       |      |

| Instantaneous Overvoltage Elements                       |      |

| Time-Delayed Dropout Overvoltage Element                 |      |

| Definite-Time Overvoltage Elements                       |      |

| Instantaneous Undervoltage Elements                      |      |

| Time-Delayed Dropout Undervoltage Elements               |      |

| Differential Overvoltage Conditions                      |      |

| Voltage Control Logic                                    |      |

| Voltage Control Instability Logic                        |      |

| Latching Bit Logic                                       |      |

| A1 Through A5 Output Contact Time-Delay Logic            |      |

| Programmable Logic Mask Concept                          |      |

| Event Reporting                                          |      |

| Metering                                                 |      |

| Self-Testing                                             |      |

| Offset                                                   |      |

| Power Supply                                             |      |

| Random-Access Memory                                     | 2-22 |

|             | Read-Only Memory                                     | 2-22 |

|-------------|------------------------------------------------------|------|

|             | Analog-to-Digital Converter                          |      |

|             | Master Offset                                        |      |

|             | Settings                                             |      |

|             | 5 <b>- 1 - 1</b>                                     | = == |

|             |                                                      |      |

|             | TABLES                                               |      |

|             |                                                      |      |

| Table 2.1:  | Logic Input Functions                                |      |

| Table 2.2:  | SEL-287V, SEL-287V-1 Relay Word                      |      |

| Table 2.3:  | SEL-287V-2 Relay Word                                |      |

| Table 2.4:  | Relay Word Bit Summary Table                         |      |

| Table 2.5:  | SEL-287V Relay Programmable Logic Masks              |      |

| Table 2.6:  | Voltage Selection for Voltage Control                |      |

| Table 2.7:  | Power Supply Self-Test Limits                        |      |

| Table 2.8:  | Self-Test Summary                                    | 2-23 |

|             |                                                      |      |

|             |                                                      |      |

|             | FIGURES                                              |      |

| Figure 2.1: | Overvoltage Elements/Undervoltage Elements and Logic | 2-10 |

| Figure 2.2: | Differential Logic (SEL-287V Relay)                  |      |

| Figure 2.3: | Voltage Differential Protection Logic (Per-Phase)    | 2-12 |

| Figure 2.4: | Voltage Differential Protection Logic (Per Phase)    |      |

| Figure 2.5: | Voltage Control Logic                                |      |

| Figure 2.6: | Voltage Control Instability Logic                    |      |

| Figure 2.7: | A1 Through A5 Output Contact Time Delay Logic        |      |

| Figure 2.8: | Basic Concept of Programmable Logic Masks            |      |

| 3 0 .       |                                                      |      |

#### **SECTION 2: SPECIFICATIONS**

#### **GENERAL SPECIFICATIONS**

**Terminal**

**Connections** Rear Screw-Terminal Tightening Torque

Minimum: 8 in-lb (0.8 Nm) Maximum: 12 in-lb (1.4 Nm)

Terminals or stranded copper wire. Ring terminals are recommended. Minimum

temperature rating of 105°C.

<u>AC</u>

<u>Input Voltage</u> 0–150 Vac rms line-to-neutral, 4-wire wye connection

Output Contact 30 A make per IEEE C37.90 para 6.7.2

<u>Current Ratings</u> 6 A carry continuously

MOV protection provided

**Optoisolated** The following optoisolated inputs draw 4 mA when nominal control voltage is

**Input Ratings** applied:

24 Vdc: 15 - 30 Vdc 48 Vdc: 30 - 60 Vdc 250 Vdc: 150 -300 Vdc

Fixed "Level-Sensitive" inputs are provided on relays with 125 Vdc optoisolated inputs. The 125 Vdc optoisolated inputs each draw 6 mA when nominal control

voltage is applied.

125 Vdc: on for 100 – 150 Vdc; off below 75 Vdc

Time

Code InputRelay accepts demodulated IRIG-B time codeCommunicationsTwo EIA-232 serial communications portsPower Supply24/48 Volt: 20-60 Vdc; < 15 watts

125/250 Volt: 85 - 350 Vdc or 85 - 264 Vac; < 15 watts

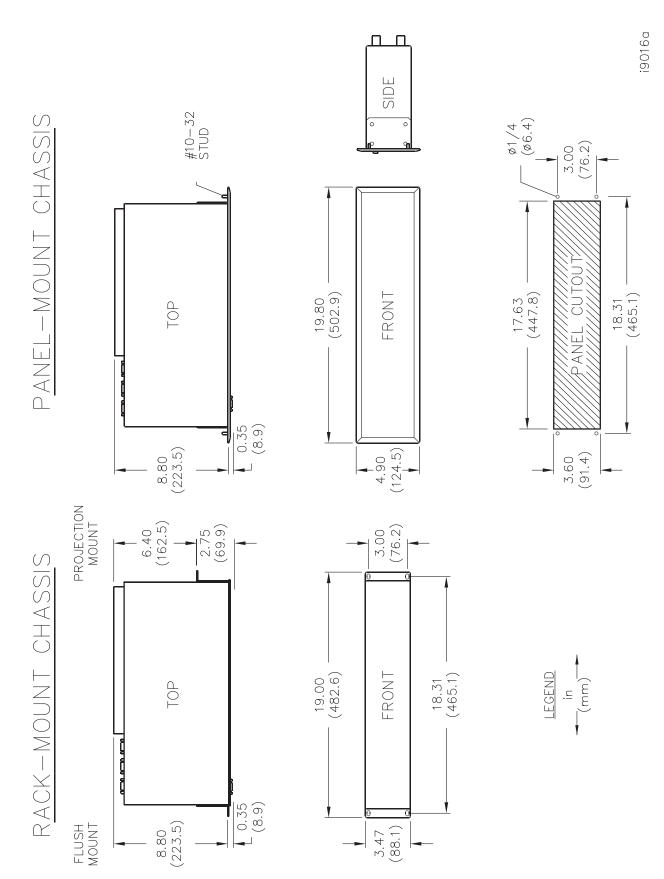

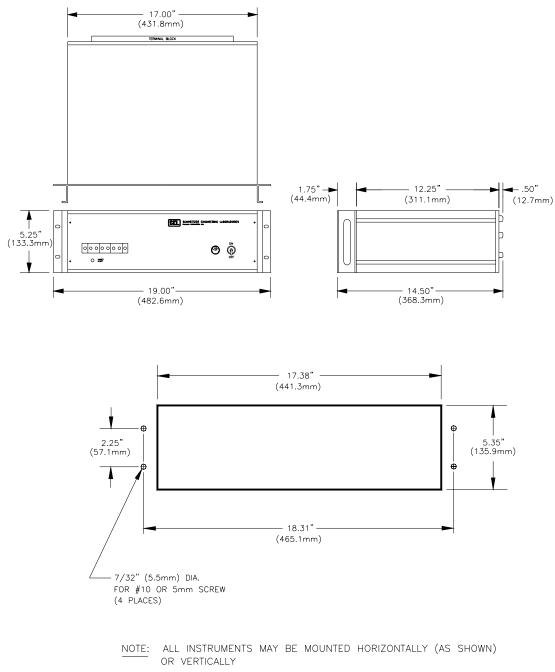

**Dimensions** 3.5" x 19" x 9" (8.89 cm x 48.2 cm x 22.86 cm) (H x W x D)

Mounts in standard EIA 19" (48.3 cm) relay rack or panel cutout. Available in

horizontal and vertical mounting configurations.

**Dielectric** Routine tested

**Strength** V inputs: 2500 Vac for 10 seconds

Other: 3000 Vdc for 10 seconds (excludes EIA-232 ports)

**Operating**

**Temperature**  $-40^{\circ}$  to  $+158^{\circ}$  F ( $-40^{\circ}$  to  $+70^{\circ}$  C)

**Environmental** IEC 68-2-30 Temperature/Humidity Cycle Test

<u>Test</u> Six-day (type tested)

InterferenceIEEE C37.90 SWC Test (type tested)TestsIEC 255-6 Interference Test (type tested)

Impulse Tests IEC 255-5 0.5 Joule, 5000 Volt Test (type tested)

**RFI Tests** Type-tested in field from a ¼-wave antenna driven by 20 watts at 150 MHz and 450

MHz, randomly keyed on and off at a distance of 1 meter from relay.

**Electrostatic**

Discharge Test IEC 801-2 (type tested)

Unit Weight 12 pounds (5.5 kg)

#### **RELAY VOLTAGE ELEMENTS**

**Voltage** 59P1, 59P2, 27P1, 27P2. These elements use the magnitude-average voltage of **Control Elements** Source X or Y, depending on the Voltage Scheme Selection setting (VSS).

Phase Over-

Voltage Elements X59A, X59B, X59C, Y59A, Y59B, Y59C

Phase Under-

Voltage Elements X27A, X27B, X27C, Y27A, Y27B, Y27C

**Definite-** X59T and Y59T with individual settings for pickup and time delay.

Time Over- X59T operates from the highest magnitude of VAX, VBX, or VCX. Y59T

**Voltage Elements** operates from the highest magnitude of VAY, VBY, or VCY.

Pickup Range 0.00–150.00 V

**Pickup Accuracy** SEL-287V-0, -2 Relays:  $\pm 0.3$  V @ 70 V, 25°C

Temperature Drift: +6 mV/°C deviation from 25°C, 70 V or

79.5 ppm/°C deviation from 25°C, 70 V, typical

Time-Delay

Range 0–64000 cycles, one-cycle steps unless otherwise noted

**Time Delay**

**Accuracy**  $\pm 0.1\% \pm 0.25$  cycle

#### RELAY VOLTAGE DIFFERENTIAL ELEMENTS

These elements test the difference between the magnitudes of like-phase voltages

taken from Sources X and Y.

Elements SEL-287V-0, -1 Relays: 87H, 87AT, 87BT, 87CT, 87AA, 87BA, 87CA

SEL-287V-2 Relay: 87H, 87T, 87A1, 87A2, 87AA, 87BA, 87CA

In the SEL-287V-2 Relay, the sign of the voltage difference determines one of two thresholds. There are no per-phase alarm threshold settings 87AA, 87BA, and

87CA, as in the SEL-287V-0, -1 Relays.

**Pickup Range** 0.00–150.00 V

Calculation

**Resolution** 0.03 V

Pickup Accuracy SEL-287V-0, -2 Relays: ± 0.63 V @ 70 V, 25°C without KSET adjustment

± 0.15 V @ 70 V, 25°C with KSET adjustment

As a result, the minimum setting should be > 0.15 V @ 70 V, 25°C and higher when the relay is exposed to higher

voltages or temperature.

SEL-287V-1 Relay: ±1.23 V @ 70 V, 25°C without KSET adjustment

$\pm$  0.30 V @ 70 V, 25°C with KSET adjustment

As a result, minimum setting should be > 0.30 V

Temperature Drift: +6 mV/°C deviation from 25°C, 70 V or 79.5 ppm/°C

deviation from 25°C, 70 V, typical

Time Delay

Range 0–64000 cycles, one-cycle steps unless otherwise noted

Time Delay

**Accuracy**  $\pm 0.1\% \pm 0.25$  cycle

#### **LOGIC INPUTS**

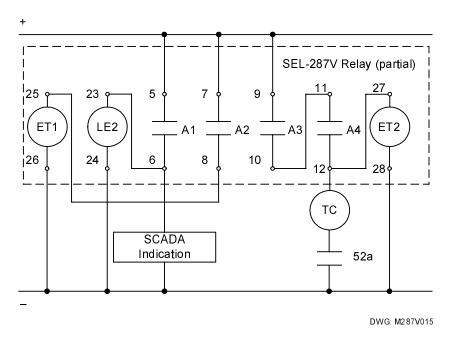

Six logic inputs control the relay functions. Assert a logic input by applying control voltage to the corresponding rear-panel contact input terminals.

**Table 2.1: Logic Input Functions**

| Input Description |                    | Function                                     |

|-------------------|--------------------|----------------------------------------------|

| RE1               | Raise Enable 1     | Enable Scheme 1 Raise Voltage Function       |

| LE1               | Lower Enable 1     | Enable Scheme 1 Lower Voltage Function       |

| RE2               | Raise Enable 2     | Enable Scheme 2 Raise Voltage Function       |

| LE2               | Lower Enable 2     | Enable Scheme 2 Lower Voltage Function       |

| ET1               | External Trigger 1 | External Event Report Trigger 1 / Reset LTCH |

| ET2               | External Trigger 2 | External Event Report Trigger 2 / Set LTCH   |

#### **RELAY OUTPUTS**

The SEL-287V Relay has seven outputs. All outputs except the ALARM output are programmed with the LOGIC command. All can be tested with the PULSE n command.

All relay contacts are rated for circuit breaker tripping duty. You may specify form "a" or "b" contacts for any of the programmable outputs or the ALARM contacts when you order the relay. The TRIP output contacts must be form "a."

#### **TRIP Output**

This output closes for any number of conditions selected by the user. The TRIP output never closes for less than the TRIP duration timer interval. After this interval, it opens when the tripping condition vanishes.

#### Programmable Outputs (A1, A2, A3, A4, A5)

These five outputs may be assigned to operate for any number of user-selected conditions.

#### **ALARM Output**

The ALARM output closes for the following conditions:

- Three unsuccessful Level 1 access attempts: one-second pulse

- Any Level 2 access attempt: one-second pulse

Self-test failures: permanent contact closure or one-second pulse depending on which self-test fails (see STATUS command).

The ALARM output also closes momentarily when settings and passwords are changed, the KSET command is executed, or a date is entered, if the year stored in EEPROM differs from the year entered (see DATE command).

The standard relay has the ALARM contacts configured as form "b". In this case it is held open during normal relay operation; it closes if control power is lost or any other alarm condition occurs.

#### **RELAY WORD**

The Relay Word consists of six eight-bit rows containing relay elements, timer outputs, and logic outputs. Each bit in the Relay Word is either a logical 1 or logical 0:

- 1 indicates that the element is picked up or logic condition is true

- 0 indicates that the element is dropped out or logic condition is false

The Logic Description defines the logic conditions in the Relay Word.

The relay updates the Relay Word each quarter-cycle.

Table 2.2: SEL-287V, SEL-287V-1 Relay Word

| Row 1 | X59A | X59B | X59C | 3Y59 | Y59A | Y59B | Y59C | 3Y59D |

|-------|------|------|------|------|------|------|------|-------|

| Row 2 | X27A | X27B | X27C | LTCH | Y27A | Y27B | Y27C | 3Y27  |

| Row 3 | X59P | X59T | Y59P | Y59T | 59P1 | 27P1 | 59P2 | 27P2  |

| Row 4 | VH1  | VL1  | VH2  | VL2  | VHD1 | VLD1 | VHD2 | VLD2  |

| Row 5 | 87H  | 87HD | LOP  | LOPD | VCI1 | VCI2 | 87T  | 87A   |

| Row 6 | 87AT | 87AA | 87BT | 87BA | 87CT | 87CA | 87TD | 87AD  |

Table 2.3: SEL-287V-2 Relay Word

| Row 1 | X59A | X59B | X59C | 3Y59 | Y59A  | Y59B | Y59C | 3Y59D |

|-------|------|------|------|------|-------|------|------|-------|

| Row 2 | X27A | X27B | X27C | LTCH | Y27A  | Y27B | Y27C | 3Y27  |

| Row 3 | X59P | X59T | Y59P | Y59T | 59P1  | 27P1 | 59P2 | 27P2  |

| Row 4 | VH1  | VL1  | VH2  | VL2  | VHD1  | VLD1 | VHD2 | VLD2  |

| Row 5 | 87H  | 87HD | LOP  | LOPD | VCI1  | VCI2 | 87T  | 87A   |

| Row 6 | 87A1 | 87AA | 87A2 | 87BA | 87A1D | 87CA | 87TD | 87A2D |

The Relay Word Bit Summary Table explains each bit in the Relay Word.

Table 2.4: Relay Word Bit Summary Table

| Row | Bit   | Definition                                   |

|-----|-------|----------------------------------------------|

| 1   | X59A  | Source X A-Phase Overvoltage                 |

|     | X59B  | Source X B-Phase Overvoltage                 |

|     | X59C  | Source X C-Phase Overvoltage                 |

|     | 3Y59  | Source Y Three-Phase Overvoltage             |

|     | Y59A  | Source Y A-Phase Overvoltage                 |

|     | Y59B  | Source Y B-Phase Overvoltage                 |

|     | Y59C  | Source Y C-Phase Overvoltage                 |

|     | 3Y59D | TDDO Source Y Three-Phase Overvoltage        |

| 2   | X27A  | Source X A-Phase Undervoltage                |

|     | X27B  | Source X B-Phase Undervoltage                |

|     | X27C  | Source X C-Phase Undervoltage                |

|     | LTCH  | Latching Bit Set by Energizing ET2 Input     |

|     | Y27A  | Source Y A-Phase Undervoltage                |

|     | Y27B  | Source Y B-Phase Undervoltage                |

|     | Y27C  | Source Y C-Phase Undervoltage                |

|     | 3Y27  | Source Y Three-Phase Undervoltage            |

| 3   | X59P  | Source X Definite-Time Overvoltage Pickup    |

|     | X59T  | Source X Definite-Time Overvoltage Trip      |

|     | Y59P  | Source Y Definite-Time Overvoltage Pickup    |

|     | Y59T  | Source Y Definite-Time Overvoltage Trip      |

|     | 59P1  | Magnitude-Average Overvoltage, Scheme 1      |

|     | 27P1  | Magnitude-Average Undervoltage, Scheme 1     |

|     | 59P2  | Magnitude-Average Overvoltage, Scheme 2      |

|     | 27P2  | Magnitude-Average Undervoltage, Scheme 2     |

| 4   | VH1   | Voltage Control Scheme 1, Voltage High State |

|     | VL1   | Voltage Control Scheme 1, Voltage Low State  |

|     | VH2   | Voltage Control Scheme 2, Voltage High State |

|     | VL2   | Voltage Control Scheme 2, Voltage Low State  |

|     | VHD1  | Scheme 1, Time-Delayed Voltage High          |

|     | VLD1  | Scheme 1, Time-Delayed Voltage High          |

|     | VHD2  | Scheme 2, Time-Delayed Voltage High          |

|     | VLD2  | Scheme 2, Time-Delayed Voltage Low           |

| Row | Bit           | Definition                                                                                                                            |

|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 5   | 87H           | High-Set Instantaneous Differential Overvoltage Trip                                                                                  |

|     | 87HD          | High-Set Time-Delayed Differential Overvoltage Trip                                                                                   |

|     | LOP           | Instantaneous Loss-of-Potential, Either Source                                                                                        |

|     | LOPD          | Time-Delayed Dropout Loss-of-Potential, Either Source                                                                                 |

|     | VCI1          | Scheme 1 Voltage Control Instability Detected                                                                                         |

|     | VCI2          | Scheme 2 Voltage Control Instability Detected                                                                                         |

|     | 87T           | Instantaneous Differential Overvoltage Trip                                                                                           |

|     | 87A           | Instantaneous Differential Overvoltage Alarm                                                                                          |

| 6   | 87AT<br>87A1  | A-Phase Differential Overvoltage Trip (SEL-287V, SEL-287V-1)<br>Differential Overvoltage Alarm, Above Tap Point (SEL-287V-2)          |

|     | 87AA          | A-Phase Differential Overvoltage Alarm                                                                                                |

|     | 87BT<br>87A2  | B-Phase Differential Overvoltage Trip (SEL-287V, SEL-287V-1)<br>Differential Overvoltage Alarm, Below Tap Point (SEL-287V-2)          |

|     | 87BA          | B-Phase Differential Overvoltage Alarm                                                                                                |

|     | 87CT<br>87A1D | C-Phase Differential Overvoltage Trip (SEL-287V, SEL-287V-1) Time-Delayed Diff. Overvoltage Alarm, Above Tap Point (SEL-287V-2)       |

|     | 87CA          | C-Phase Differential Overvoltage Alarm                                                                                                |

|     | 87TD          | Time-Delayed Differential Overvoltage Trip                                                                                            |

|     | 87AD<br>87A2D | Time-Delayed Differential Overvoltage Alarm (SEL-287V, SEL-287V-1) Time-Delayed Diff. Overvoltage Alarm, Below Tap Point (SEL-287V-2) |

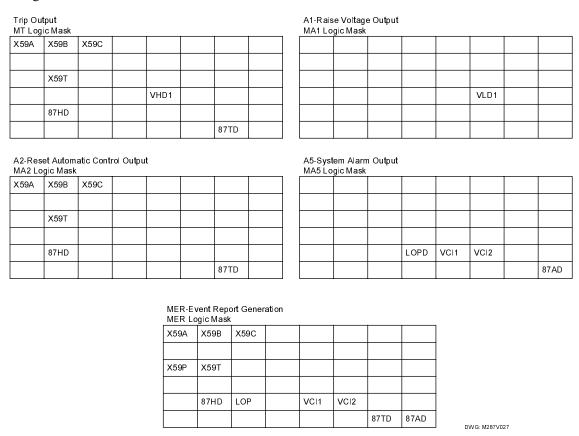

#### PROGRAMMABLE LOGIC MASKS

The relay uses programmable logic masks to control tripping, programmable output contacts, and event report generation. Logic masks are saved in nonvolatile memory with the other settings. They are set with the LOGIC command and retained through losses of control power.

Programmable logic masks and their functions appear in Table 2.5.

Table 2.5: SEL-287V Relay Programmable Logic Masks

| Mask | Function                         |  |

|------|----------------------------------|--|

| MT   | Controls TRIP output contacts    |  |

| MA1  | Controls A1 output contact       |  |

| MA2  | Controls A2 output contact       |  |

| MA3  | Controls A3 output contact       |  |

| MA4  | MA4 Controls A4 output contact   |  |

| MA5  | MA5 Controls A5 output contact   |  |

| MER  | Triggers Event Report Generation |  |

#### **OUTPUT LOGIC**

Six of the seven outputs are programmable with masks (MT, MA1, MA2, MA3, MA4, MA5) that select Relay Word bits to control outputs.

The equations for the outputs follow:

```

TRIP = R * MT (where R is the Relay Word array)

Close TRIP contact = TRIP

Open TRIP contact = NOT(TRIP) * NOT(Minimum Trip Duration timer (TDUR))

A1 = R * MA1

A2 = R * MA2

A3 = R * MA3

A4 = R * MA4

A5 = R * MA5

```

"\*" indicates the bitwise "AND" operator, which "ANDs" each Relay Word bit with the mask bit in the same position in the 6x8 mask array to determine contact operation.

All output relays are rated for tripping duty. The TRIP output relay has two "a" type contacts. Each of the other six relays has a single contact.

#### **RELAY TARGETS**

The relay normally displays the targets identified on the front panel. Under normal operating conditions, the enable (EN) target lamp is lit. If the relay trips, it illuminates the LED corresponding to the element asserted at the time of trip. The target LEDs latch. The target LEDs that illuminated during the last trip remain lit until one of the following occurs:

- Next trip occurs

- Operator presses front-panel TARGET RESET button

- Operator executes TARGET R command

When a new trip occurs, the targets clear and the LEDs display the most recent tripping target.

When you press the TARGET RESET button, all eight indicators illuminate for a one-second lamp test. The relay targets clear and the Enable light (EN) illuminates to indicate that the relay is operational.

Use the TARGET command and display to examine the state of the relay inputs, outputs, and Relay Word elements. For more details, see *Command Descriptions* in *Section 3: Communications*.

#### SERIAL INTERFACES

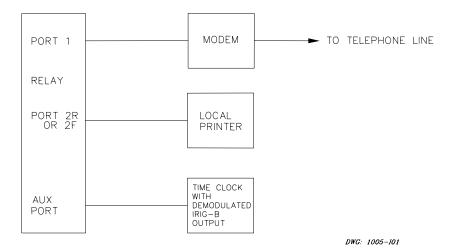

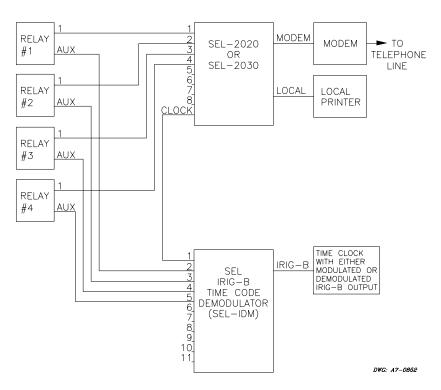

Connectors labelled PORT 1 and PORT 2 are EIA-232 serial data interfaces. Generally, PORT 1 is used for remote communications via a modem, while PORT 2 is used for local communications via a terminal or SEL-PRTU protective relay terminal unit.

The baud rate of each port is set by jumpers near the front of the main board. You can access these jumpers by removing either the top cover or front panel. Available baud rates are 300, 600, 1200, 2400, 4800, and 9600.

The serial data format is:

Eight data bits

Two stop bits (-E2 model) or one stop bit (-E1 model)

No parity

You will receive a relay with two stop bits (-E2 model) unless you specifically request one stop bit (-E1 model). To determine whether your relay has one or two stop bits, look at the last two characters of the relay firmware identification number (FID). Use the EVENT command (see **Section 4: Event Reporting**) to obtain an event report that includes the firmware identification number.

The serial communications protocol appears in *Section 3: Communications*.

The SEL-287V Relay includes front- and rear-panel connectors for PORT 2. When a communication device is connected to the front-panel port, the relay ignores input from the rear-panel port. When the front-panel communications cable is removed, the relay resumes normal communications with the device connected to the rear-panel port.

#### **IRIG-B INPUT DESCRIPTION**

The port labelled J201/AUX INPUT receives demodulated IRIG-B time-code input. The IRIG-B input circuit is a 56-ohm resistor in series with an optocoupler input diode. The input diode has a forward drop of about 1.5 V. Driver circuits should put approximately 10 mA through the diode when "on."

The IRIG-B serial data format consists of a one-second frame containing 100 pulses and divided into fields. The relay decodes second, minute, hour, and day fields and sets the relay clock accordingly.

When IRIG-B data acquisition is activated either manually (with the IRIG command) or automatically, the relay reads two consecutive frames. It updates the older frame by one second and compares the frames. If they do not agree, the relay considers the data erroneous and discards it.

The relay reads the time code automatically about once every five minutes. The relay stops IRIG-B data acquisition 10 minutes before midnight on New Year's Eve so the relay clock may implement the year change without interference from the IRIG-B clock. Ten minutes after midnight, the relay restarts IRIG-B data acquisition.

#### SIGNAL PROCESSING

The relay low-pass filters all six voltage channels and samples the channels four times per power system cycle. The microprocessor digitally filters each voltage channel using the CAL digital filter explained below. The relay stores the digital filter output for event reporting and magnitude calculations.

The microprocessor uses the digital filter output to determine the magnitude of each voltage. Magnitudes and differentials are smoothed over one cycle by an averaging function. Relay elements use the filtered and smoothed voltage magnitudes.

The relay uses a simple, effective CAL digital filter with the properties of a double differentiator smoother. Let the latest four samples of one analog channel be X1, X2, X3, and X4. Then the filter is defined:

$$P = X1 - X2 - X3 + X4$$

.

This filter eliminates dc offsets. When all samples are set to the same value, the filter output is zero. The filter also eliminates ramps, which you may verify by setting the samples equal to 1, 2, 3, 4. Again, the output is zero.

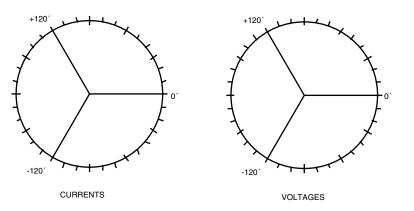

Every quarter-cycle, the relay computes a new value of x for each input. The current value of x combines with the previous value (renamed y) to form a Cartesian coordinate pair. This pair represents the input signal as a phasor (x, y). The relay processes these phasor representations of the input signals. They also appear with the relay output after an event. You can use the data to construct phasor diagrams of the voltages.

#### LOGIC DESCRIPTION

#### Overvoltage/Undervoltage Logic

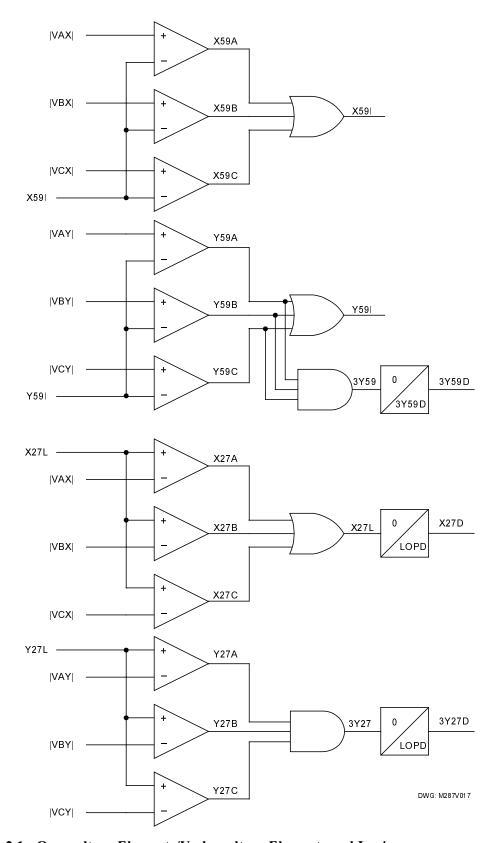

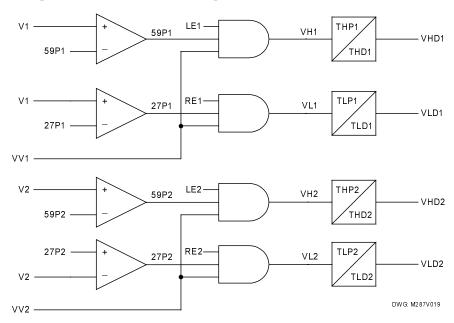

Figure 2.1 shows the logic diagram for the over-/undervoltage elements. The relay compares magnitudes of the six input quantities against user-settable thresholds. The individual phase overvoltage outputs (e.g., X59A, X59B, X59C) provide instantaneous overvoltage protection.

Output 3Y59 indicates a three-phase overvoltage condition on the Source Y inputs. This output drives an instantaneous pickup/time-delay dropout timer to produce output 3Y59D.

Output X27L indicates an undervoltage condition on any one or more phases of the Source X inputs. This output drives an instantaneous pickup/time-delay dropout timer to produce output X27D.

Output 3Y27 indicates a three-phase undervoltage condition on the Source Y inputs. This output drives an instantaneous pickup/time-delay dropout timer to produce output 3Y27D.

Outputs X27D and 3Y27D control selection of voltage sources for the voltage control logic. When the undervoltage elements drop out, the relay declares the input voltages valid for voltage control. The X and Y dropout time delay, LOPD, allows input voltages to stabilize before they are used by the voltage control logic.

Figure 2.1: Overvoltage Elements/Undervoltage Elements and Logic

#### **Loss-of-Potential Logic**

Outputs X27D and 3Y27D are OR-ed together to indicate a loss-of-potential (LOP) condition.

The output of the LOP time-delay dropout timer (LOPD) supervises the differential voltage elements to ensure that they operate only when both three-phase voltage input sources are valid.

The LOPD dropout delay allows voltage sources and elements to stabilize before the differential element outputs are considered valid. This delay permits successful capacitor bank energization.

Setting X27L or Y27L to zero ensures that the corresponding undervoltage elements do not pick up, even for a zero-voltage input condition. This is useful in disabling LOPD for either X or Y potentials.

#### **Definite-Time Overvoltage Logic**

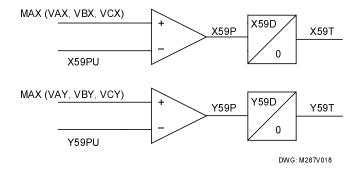

Figure 2.2 shows the logic for the definite-time overvoltage function.

For Source X, when the magnitude of VAX, VBX, or VCX rises above the X59PU setting, the X59P element asserts and starts the X59D timer. When the X59D timer expires, the X59T element asserts. Source Y protection operates similarly.

Instantaneous elements X59P and Y59P and time-delayed elements X59T and Y59T are available in the Relay Word for tripping, alarming, and event report triggering.

Figure 2.2: Differential Logic (SEL-287V Relay)

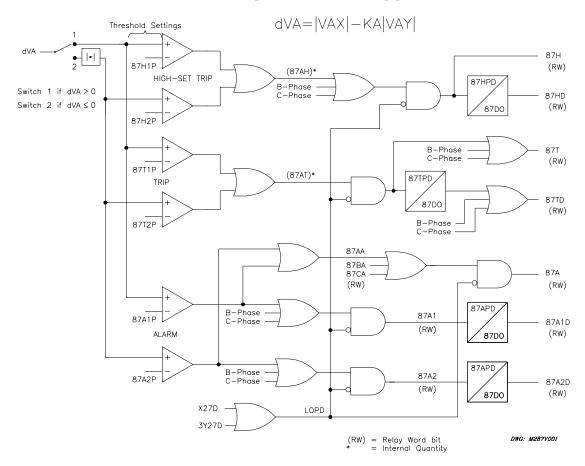

#### Voltage Differential Logic (SEL-287V, SEL-287V-1 Relays)

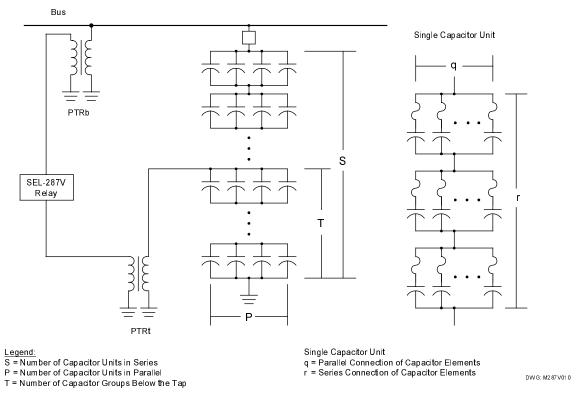

Figure 2.3 shows the logic for the voltage differential protection scheme. The voltage differential elements provide protection for capacitor bank faults that produce a differential voltage at the bus and tap PT secondaries. The magnitude differences dVA, dVB, and dVC are calculated with independent ratio factors KA, KB, and KC. For example, dVA is calculated:

$$|dVA| = ||VAX| - KA|VAY||$$

Figure 2.3: Voltage Differential Protection Logic (Per-Phase)

The relay tests the magnitude of each difference against user-settable trip and alarm thresholds on a per-phase basis. The three ratio adjustment constants (KA, KB, and KC) are independent, permitting differential relay unbalance nulling on a per-phase basis. There are three independent alarm threshold settings (87AA, 87BA, and 87CA), one per phase. The independent trip threshold settings (87T and 87H) are common for all phase elements.

The METER command output contains signed voltage differences so you can adjust ratio factors to null voltage differences under balanced conditions. You may also use the KSET command to calculate and adjust the ratio factors automatically (see *KSET n*, *Section 3: Communications*).

The LOPD (loss-of-potential, delayed dropout) signal supervises the 87A, 87T, and 87H differential elements.

A differential voltage condition on any phase starts the timer for that phase. If the condition continues through the duration of the timer, the timer output (87AD, 87TD, or 87HD) asserts. The output remains asserted for a settable dropout delay after the timer input deasserts.

The 87HD and 87TD logic provides independently operated, identically set time delays for each phase.

The Relay Word contains the single-phase outputs from differential elements 87T and 87A; three-phase LOPD-supervised signals 87A, 87T, and 87H; and the time-delayed outputs 87AD, 87TD, and 87HD.

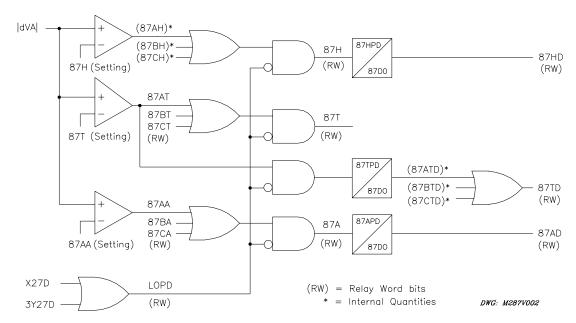

#### Voltage Differential Logic (SEL-287V-2 Relays)

Figure 2.4 shows the logic for the voltage differential protection scheme. The voltage differential elements provide protection for capacitor bank faults that produce a differential voltage at the bus and tap PT secondaries. The differences dVA, dVB, and dVC are calculated with independent ratio factors KA, KB, and KC as shown below:

$$dVA = |VAX| - KA|VAY|$$

$$dVB = |VBX| - KB|VBY|$$

$$dVC = |VCX| - KC|VCY|$$

The independent ratio factors (KA, KB, and KC) permit voltage unbalance nulling on a per-phase basis.

The relay uses the sign of dVA, in Figure 2.4, to determine which group of thresholds to use for comparison. If dVA > 0, it uses thresholds 87H1P, 87T1P, and 87A1P for high-set trip, trip, and alarm, respectively. If  $dVA \le 0$ , it uses 87H2P, 87T2P, and 87A2P. In either case, the relay compares the absolute value of dVA to the selected thresholds. Identical comparisons are performed for B- and C-phases using dVB and dVC.

Thresholds 87A1P and 87T1P are used for blown-fuse detection above the tap point. 87A1P is set to alarm for one fuse operation and 87T1P to trip for several fuse operations that could produce voltage overstress of the remaining cans in the series group. Thresholds 87A2P and 87T2P serve the same functions for fuse operations below the tap point.

Figure 2.4: Voltage Differential Protection Logic (Per Phase)

Thresholds 87H1P (dVA > 0) and 87H2P (dVA  $\leq$  0) can be used either for high-speed tripping for excessive numbers of fuse operations (much like the regular alarm and trip functions) or for catastrophic events such as a complete series group flashover. If used for fuse detection, 87H1P applies above the tap and 87H2P below the tap. If used for group flashover, 87H1P applies below the tap and 87H2P above the tap.

The METER command output contains signed voltage differences, so you can adjust ratio factors to null voltage differences under balanced conditions. You may also use the KSET command to calculate and adjust the ratio factors automatically (see *KSET n*, *Section 3: Communications*).

The LOPD (loss-of-potential, delayed dropout) signal supervises the 87A, 87A1, 87A2, 87T, and 87H differential elements.

A differential voltage condition on any phase starts a timer. If the condition continues through the duration of the timer, the timer output 87A1D, 87A2D, 87TD, or 87HD asserts. For the 87TD output, there are three separate timers, one for each phase. The output remains asserted for a settable dropout delay after the timer input deasserts. The high-set pickup timer value is setting 87HPD; the trip timer pickup for each phase is 87TPD; and the above/below alarm timer pickups are both 87APD. A common dropout timer value 87DO applies to all six timers.

The Relay Word contains outputs from several points in the voltage differential logic. These points are indicated by (RW) below the bit names in Figure 2.4. Logic for the major differential element Relay Word bits is shown below in equation form.

#### **Differential Overvoltage Conditions**

```

LOPD =

X27D + 3Y27D

87H

NOT(LOPD) * (87AH + 87BH + 87CH)

87T

NOT(LOPD) * 87AT + NOT(LOPD) * 87BT + NOT(LOPD) * 87CT

NOT(LOPD) * (87AA + 87BA + 87CA)

87A

=

87H * (87HPD pickup delay, 87DO dropout delay)

87HD

NOT(LOPD) * 87AT * (87TPD pickup delay, 87DO dropout delay)

87TD

+ NOT(LOPD) * 87BT * (87TPD pickup delay, 87DO dropout delay)

+ NOT(LOPD) * 87CT * (87TPD pickup delay, 87DO dropout delay)

87A1 * (87APD pickup delay, 87DO dropout delay)

87A1D

87A2 * (87APD pickup delay, 87DO dropout delay)

87A2D =

```

#### **Voltage Control Logic**

Figure 2.5 illustrates voltage control logic. The SEL-287V Relay includes two identical three-phase over-/undervoltage measurement and timing networks. One network is driven by V1; the other is driven by V2. V1 and V2 are either VX or VY, depending on the Voltage Selection Scheme chosen and voltage conditions. VX and VY are the magnitude averages of the three-phase source inputs:

```

VX = 1/3 (|VAX| + |VBX| + |VCX|)

VY = 1/3 (|VAY| + |VBY| + |VCY|)

```

Consider the scheme for voltage V1. The relay tests the three-phase magnitude average voltage V1 against two thresholds: 59P1 and 27P1. The under-/overvoltage conditions are supervised by signal VV1 (Valid Voltage condition 1, described later) and by external inputs LE1 (Lower Enable 1) or RE1 (Raise Enable 1).

The outputs VH1 and VL1 drive timers with independent time-delay pickup and dropout settings to produce outputs VHD1 and VLD1. Output VHD1 can drive a contact for lowering system voltage (e.g., tripping a capacitor bank or inserting a reactor bank) with the permission of external

input LE1. Output VLD1 is intended to drive a contact for raising system voltage (e.g., inserting a capacitor bank or tripping a reactor bank) with the permission of external input RE1.

The scheme for voltage V2 is identical to that for V1. The two schemes have independent settings and independent raise/lower enable inputs.

Figure 2.5: Voltage Control Logic

#### **Voltage Selection Scheme**

Table 2.6 shows voltage selection settings for the voltage control schemes described above. Setting VSS (Voltage Selection Scheme) selects one of three ways the relay applies magnitude-average input voltages VX and/or VY to voltage control inputs V1 and V2.

$$VSS = I$$

If the two voltage control schemes (1 and 2) are to be independent, set VSS=I (independent). With this setting the relay applies VX to the V1 input and VY to the V2 input. This assignment does not depend on the voltage conditions. The valid voltage condition for scheme 1 is VV1 = not(X27D) + not(LOPE1). The voltage control logic requires either no loss-of-potential condition for Source X, or that loss-of-potential checking be disabled by setting LOPE1 = N. A similar logic applies to Scheme 2.

$$VSS = B$$

When setting VSS = B (relay selects the better source), the relay normally sets V1 = VX. If Source X is bad (X27D asserts) and Source Y is still good (3Y27D is deasserted), the relay sets V1 = VY, so voltage control Scheme 1 operates from Source Y.

Similarly, the relay normally sets V2 = VY. However, if Source Y is bad while Source X is good, V2 = VX.

When dissimilar nominal secondary voltages are input to Source X and Source Y, do not apply a setting VSS = B.

Under some conditions, you may wish to use Source X for both V1 and V2. To do so, set VSS = X. Then the relay sets V1 = V2 = VX for all conditions. The voltage valid condition is true when X27D is not asserted and depends on LOPE1 when X27D is asserted.

**Table 2.6: Voltage Selection for Voltage Control**

| Setting<br>VSS | Voltage<br>Source | Voltage Conditions     | Voltage Control Inputs                                         |           |

|----------------|-------------------|------------------------|----------------------------------------------------------------|-----------|

| VSS=I          | X, Y              | Independent            | V1=VX V2=VY VV1=not(X27D)+not(LOPE1) VV2=not(3Y27D)+not(LOPE2) |           |

|                |                   |                        |                                                                |           |

|                |                   |                        |                                                                |           |

|                |                   |                        |                                                                |           |

| VSS=B          | Better<br>Source  | not(X27D) * not(3Y27D) | V1=VX<br>V2=VY                                                 | VV1=VV2=1 |

|                |                   | not(X27D) * 3Y27D      | V1=V2=VX                                                       | VV1=VV2=1 |

|                |                   | X27D * not(3Y27D)      | V1=V2=VY                                                       | VV1=VV2=1 |

|                |                   | X27D * 3Y27D           | V1=VX<br>VV1=not(LOPE1)<br>VV2=not(LOPE2)                      | V2=VY     |

| VSS=X          | Source X<br>Only  | not(X27D)              | V1=V2=VX<br>VV1=VV2=1                                          |           |

|                |                   | X27D                   | V1=V2=VX<br>VV1=VV2=not(LOPE1)                                 |           |

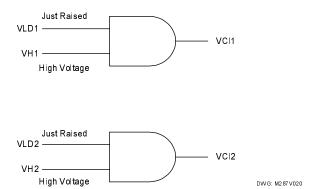

#### **Voltage Control Instability Logic**

The two AND gate outputs in Figure 2.6 indicate voltage control instability. When a signal to decrease voltage (VH1) occurs before the increase-voltage dropout time (TLD1) expires, the relay asserts VCI1. When the relay asserts VCI1 or VCI2 bits, voltage control action probably is causing a voltage change greater than the amount between the raise and lower voltage settings.

Outputs VCI1 and VCI2 are in the Relay Word. They may be used to alarm or lock out voltage control via an external latching relay, or be included in the MT mask to trip and lock the bank out of service when instability conditions occur.

Figure 2.6: Voltage Control Instability Logic

#### **Latching Bit Logic**

When relay setting LTCHE = Y, the External Trigger inputs are used to set and reset a latch bit, LTCH, in the Relay Word. Assert LTCH by energizing ET2; LTCH does not reset until ET1 is energized and ET2 is deenergized.

This feature can be used for SCADA alarm indication and enabling the voltage control logic for automatic load restoration.

Note that when LTCHE = Y, ET1 and ET2 do not trigger event records.

When LTCHE = N, assert ET1 and ET2 to trigger event reports. The LTCH bit does not operate when LTCHE = N.

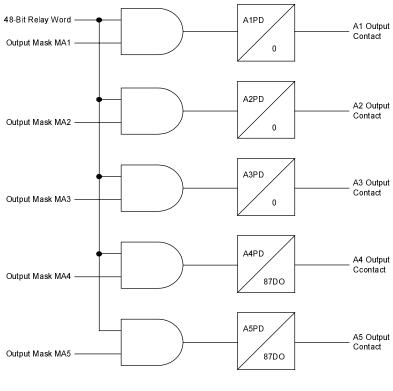

#### A1 Through A5 Output Contact Time-Delay Logic

Figure 2.7 illustrates the A1 through A5 output contact time-delay logic. Output from the A1 through A5 contacts can be delayed through A1PD, A2PD, A3PD, A4PD, and A5PD time-delay pickup timers. The A1 through A3 output contacts open as soon as the conditions set in the A1, A2, or A3 logic mask reset. The 87DO time-delay dropout timer holds the contact closed for a set time delay after the condition in the A4 or A5 mask resets.

DWG: M287V021

Figure 2.7: A1 Through A5 Output Contact Time Delay Logic

#### INTERMEDIATE LOGIC

The logic equations shown below represent combinations of the relay elements and other conditions. In the following equations the "\*" indicates a logical "AND," while the "+" indicates a logical "OR."

#### **Instantaneous Overvoltage Elements**

X59I = X59A + X59B + X59C

Y59I = Y59A + Y59B + Y59C

3Y59 = Y59A \* Y59B \* Y59C

**Note:** X59I and Y59I are used for targeting purposes only.

#### **Time-Delayed Dropout Overvoltage Element**

3Y59D = 3Y59 \* (inst pickup, 3Y59D dropout delay)

#### **Definite-Time Overvoltage Elements**

X59T = X59P \* (X59D pickup delay) Y59T = Y59P \* (Y59D pickup delay)

#### **Instantaneous Undervoltage Elements**

```

X27L = X27A + X27B + X27C

3Y27 = Y27A * Y27B * Y27C

```

#### **Time-Delayed Dropout Undervoltage Elements**

```

X27D = X27L * (inst pickup, LOPD dropout delay)

3Y27D = 3Y27 * (inst pickup, LOPD dropout delay)

```

#### **Differential Overvoltage Conditions**

**Note:** Relay Word elements displayed in bold type.

```

LOPD =

X27D + 3Y27D

87AH

dVA > 87Hsetting

87BH

dVB > 87Hsetting

=

87CH

dVC > 87Hsetting

87AT

dVA > 87Tsetting

87BT

=

dVB > 87Tsetting

dVC > 87Tsetting

87CT

87AA

|dVA| > 87AAsetting

87BA

dVB > 87BAsetting

dVC > 87CA setting

87CA

87H =

NOT(LOPD) * (87AH + 87BH + 87CH)

87T =

NOT(LOPD) * (87AT + 87BT + 87CT)

87A =

NOT(LOPD) * (87AA + 87BA + 87CA)

87ATD =

NOT(LOPD) * 87AT * (87TPD pickup delay, 87DO dropout delay)

NOT(LOPD) * 87BT * (87TPD pickup delay, 87DO dropout delay)

87BTD =

87CTD =

NOT(LOPD) * 87CT * (87TPD pickup delay, 87DO dropout delay)

87H * (87HPD pickup delay, 87DO dropout delay)

87HD

87TD

87ATD + 87BTD + 87CTD

87A * (87APD pickup delay, 87DO dropout delay)

87AD

```

#### **Voltage Control Logic**

```

VH1= LE1 * 59P1 * VV1

VL1= RE1 * 27P1 * VV1

VH2= LE2 * 59P2 * VV2

VL2= RE2 * 27P2 * VV2

```

The states of VV1 and VV2 are determined from the VSS setting and the voltage conditions as shown in Table 2.6.

```

VHD1 = VH1 * (THP1 pickup delay, THD1 dropout delay)

VLD1 = VL1 * (TLP1 pickup delay, TLD1 dropout delay)

```

```

VHD2 = VH2 * (THP2 pickup delay, THD2 dropout delay)

VLD2 = VL2 * (TLP2 pickup delay, TLD2 dropout delay)

```

#### **Voltage Control Instability Logic**

VCI1 = VLD1 \* VH1VCI2 = VLD2 \* VH2

#### **Latching Bit Logic**

```

Set LTCH = ET2

Reset LTCH = ET1 * NOT(ET2)

```

This logic is enabled when LTCHE = Y. When LTCHE = N, ET1 and ET2 act as external event triggers.

#### A1 Through A5 Output Contact Time-Delay Logic

```

A1TD = A1 * (A1PD Pickup delay, instantaneous dropout delay)

A2TD = A2 * (A2PD Pickup delay, instantaneous dropout delay)

A3TD = A3 * (A3PD Pickup delay, instantaneous dropout delay)

A4TD = A4 * (A4PD pickup delay, 87DO dropout delay)

A5TD = A5 * (A5PD pickup delay, 87DO dropout delay)

```

#### PROGRAMMABLE LOGIC MASK CONCEPT

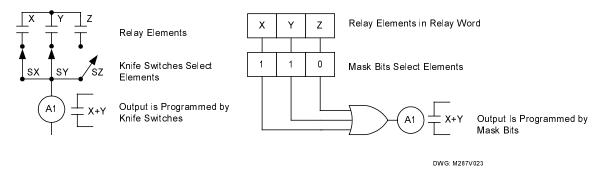

Figure 2.8 illustrates the programmable logic mask concept by comparing it to the connections of discrete relay elements. At the top, the figure shows relay element contacts X, Y, and Z connected to a common reference, such as the positive pole of the battery. The ends of these contacts are connected to knife switches, and the other side of each switch connects to drive an auxiliary relay labelled A1. The knife switch positions select which relay elements can pick up the auxiliary relay. In the figure switches SX and SY are closed, so closure of contact X or contact Y causes A1 to pick up. This is expressed in Boolean terms next to the A1 output contact by the notation X + Y, where "+" indicates the logical "OR" operation.

Figure 2.8: Basic Concept of Programmable Logic Masks

This logic scheme may be modified by setting switches SX, SY, and SZ to other positions. If an application requires combinations of contacts X, Y, and Z to control other auxiliary relays, diodes must be used in each contact path. These diodes ensure that the logic settings for this scheme do not affect other auxiliary relays.

In programmable mask logic the states of all relay elements are collected into a single group of binary digits called the Relay Word. Each bit reports the state of one relay element. A zero indicates that the element is not picked up; a one indicates that the element is picked up.

Figure 2.8 shows a three-bit Relay Word with elements X, Y, and Z. Each bit corresponds to one relay element contact in the contact-logic equivalent. The operator sets or clears bits in the mask for the A1 output rather than using switches to select which elements control the A1 output (see *Section 3: Communications, LOGIC n*). In the figure the operator selected the X and Y elements and deselected the Z element by setting the mask bits to (1, 1, 0). The computer ANDs each bit in the Relay Word with the corresponding bit set in the mask. Next, it ORs all three outputs together, forming the condition that drives the output relay A1. A convenient shorthand way of expressing this bitwise AND followed by an OR operation is:

$$A1 = R * MA1$$

where R is the Relay Word (X, Y, Z), MA1 is the mask (1, 1, 0), and "\*" indicates the operation of bitwise ANDing followed by the OR operation.

While the mask elements are fixed, the Relay Word updates each quarter-cycle. In this example, if the X or Y element is set to (1) in the Relay Word, the A1 contact closes. The state of the A1 contact is independent of the Z element in the Relay Word because the corresponding Z element in the mask equals zero.

The relay has user-programmable logic masks that control tripping, programmable output contacts, and event report generation. The logic masks are saved in nonvolatile memory with the other settings and retained through losses of control power.

#### **EVENT REPORTING**

The relay retains a data record for each of the 12 most recent events. The record includes input voltages, Relay Word elements, input contacts, and output contacts. The relay saves a report when any of the following occur:

- The relay trips

- User-selected Relay Word bits assert

- User executes the TRIGGER command

- ET1 or ET2 input is asserted (if LTCHE = N)

**Section 4: Event Reporting** has further information regarding the generation, content, and analysis of event reports saved by the relay.

#### **M**ETERING

The meter function shows the current value of ac voltage input magnitudes and phase differential voltage magnitudes (see **Section 3: Communications**, **METER n**). You can execute this command locally or remotely to check bus and bank conditions.

#### **SELF-TESTING**

The relay runs a variety of self-tests. Some tests have warning and failure states; others only have failure states. The relay generates a status report after any self-test warning or failure.

The relay closes the ALARM contacts after any self-test fails. When the relay detects certain failures, it disables the breaker control functions and places the output relay driver port in an input mode. No outputs may be asserted when the relay is in this configuration. The relay runs all self-tests at least every five minutes.

#### Offset

The relay measures the dc offset voltage of each analog input channel and compares the value against fixed limits. If an offset measurement is outside the fixed limits, the relay declares a warning or failure.

#### **Power Supply**

The relay measures the internal power supply voltages and compares the values against fixed limits. If a voltage measurement is outside the limits, the relay declares a warning or failure.

| Supply | Warning Thresholds |         | Failure Thresholds |         |

|--------|--------------------|---------|--------------------|---------|

| +5 V   | 5.3 V              | 4.7 V   | 5.4 V              | 4.6 V   |

| +15 V  | 15.8 V             | 14.2 V  | 16.2 V             | 13.8 V  |

| -15 V  | -15.8 V            | -14.2 V | -16.2 V            | -13.8 V |

**Table 2.7: Power Supply Self-Test Limits**

#### **Random-Access Memory**

The relay completely checks the random-access memory (RAM) every 35 seconds. If a byte cannot be written to or read from, the relay declares a RAM failure. There is no warning state for this test.

#### **Read-Only Memory**

The relay checks the read-only memory (ROM) by computing a checksum. If the computed value does not agree with the stored value, the relay declares a ROM failure. There is no warning state for this test.

#### **Analog-to-Digital Converter**

The relay verifies the A/D converter function by checking the A/D conversion time. The test fails if conversion time is excessive or a conversion starts and never finishes. There is no warning state for this test.

## **Master Offset**

The master offset (MOF) test checks the dc offset in the multiplexer/analog to digital converter circuit. The relay selects a grounded input to sample for dc offset.

## **Settings**

Every time you set the relay, it calculates a checksum for the settings. The checksum is stored in nonvolatile memory with the settings. The relay recalculates and compares the checksum at least every five minutes. If the checksums disagree, the setting test fails and the relay disables all protective and control functions.

Table 2.8 shows relay actions for any self-test condition: warning (W) or failure (F).

**Table 2.8: Self-Test Summary**

| Self-Test          | Limits           | Status<br>Message | Protection<br>Disabled | Control<br>Disabled | Alarm<br>Output                    |

|--------------------|------------------|-------------------|------------------------|---------------------|------------------------------------|

| RAM                |                  | F                 | YES                    | YES                 | permanent closure                  |

| ROM                |                  | F                 | YES                    | YES                 | permanent closure                  |

| Settings           |                  | F                 | YES                    | YES                 | permanent closure                  |

| A/D                |                  | F                 | YES                    | no                  | permanent closure                  |

| +5 V               | ±0.3 V<br>±0.4 V | W<br>F            | no<br>YES              | no<br>YES           | no ALARM closure permanent closure |

| ±15 V              | ±0.8 V<br>±1.2 V | W<br>F            | no<br>YES              | no<br>no            | no ALARM closure permanent closure |

| Channel<br>Offsets | ±50 mV<br>±75 mV | W<br>F            | no<br>no               | no<br>no            | no ALARM closure one-second pulse  |

| Master<br>Offset   | ±50 mV<br>±75 mV | W<br>F            | no<br>no               | no<br>no            | no ALARM closure one-second pulse  |

# **TABLE OF CONTENTS**

| SECTIO      | ON 3: COMMUNICATIONS                                    | 3-1  |

|-------------|---------------------------------------------------------|------|

| Intr        | roduction                                               | 3-1  |

|             | rial Port Connections and Configurations                |      |

|             | mmunications Protocol                                   |      |

|             | mmand Characteristics                                   |      |

|             | Startup                                                 |      |

|             | Command Format                                          |      |

| Cor         | mmand Descriptions                                      |      |

|             | Access Level 0 Command                                  |      |

|             | ACCESS                                                  |      |

|             | Access Level 1 Commands                                 |      |

|             | 2ACCESS                                                 |      |

|             | DATE mm/dd/yy                                           |      |

|             | EVENT n                                                 |      |

|             | HISTORY                                                 |      |

|             | IRIG                                                    |      |

|             | METER n                                                 |      |

|             | QUIT                                                    |      |

|             | SHOWSET                                                 |      |

|             | STATUS                                                  |      |

|             | TARGET n k                                              |      |

|             | TIME hh:mm:ss                                           |      |

|             | TRIGGER                                                 |      |

|             | Access Level 2 Commands                                 |      |

|             | KSET n                                                  |      |

|             | LOGIC n                                                 |      |

|             | PASSWORD (1 or 2) password                              |      |

|             | PULSE n                                                 |      |

|             | SET n                                                   |      |

| SEI         | L-287V Voltage Differential Relay Command Summary       |      |

|             | TABLES                                                  |      |

| T. 1.1. 2.1 |                                                         | 2.0  |

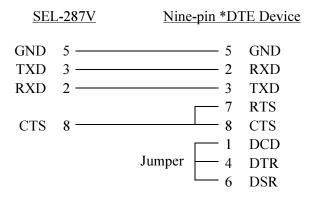

| Table 3.1:  | SEL-287V Relay Serial Port Connector Pin Assignments    |      |

| Table 3.2:  | Event Type Selection                                    |      |

| Table 3.3:  | Hexadecimal/Binary Conversion                           |      |

| Table 3.4:  | Target LED Assignment (SEL-287V, SEL-287V-1 Relays)     |      |

| Table 3.5:  | Target LED Assignment (SEL-287V-2 Relay)                | 3-13 |

|             | FIGURES                                                 |      |

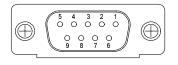

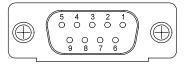

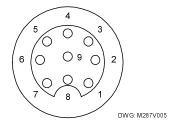

| Figure 3.1: | SEL-287V Relay Nine-Pin Connector Pin Number Convention | 3-2  |

#### **SECTION 3:** COMMUNICATIONS

## INTRODUCTION

The relay is set and operated via serial communications interfaces connected to a computer terminal and/or modem or the SEL-PRTU. Communication serves these purposes:

- Relay responds to commands spanning all functions, e.g., setting, metering, and control operations.

- Relay generates an event record for assertions of the TRIP output, either External Trigger input, and any element set in the programmable logic mask MER.

- Relay transmits messages in response to changes in system status, e.g., self-test warning.

Two password-protected access levels provide security against unauthorized access and setting changes.

It is impossible to disable any relaying or control functions via communications, unless a user enters erroneous or improper settings with the SET or LOGIC commands.

**Note:** In this manual, commands to type appear in bold/upper case: **OTTER**. Keys to press appear in bold/upper case/brackets: **<ENTER>**.

Relay output appears in the following format and font:

| -  |                  |              |                | • • |

|----|------------------|--------------|----------------|-----|

|    | Example Settings | Date: 6/1/92 | Time: 01:01:01 |     |

| ١. |                  |              |                |     |

## SERIAL PORT CONNECTIONS AND CONFIGURATIONS

The SEL-287V Relay is equipped with two EIA-232 serial communications ports. PORT 2 has 9-pin connectors on both the front and rear panels, designated PORT 2F and PORT 2R, respectively.