# SEL-2BFR, -2/BFR

# **BREAKER FAILURE RELAY AND MONITOR**

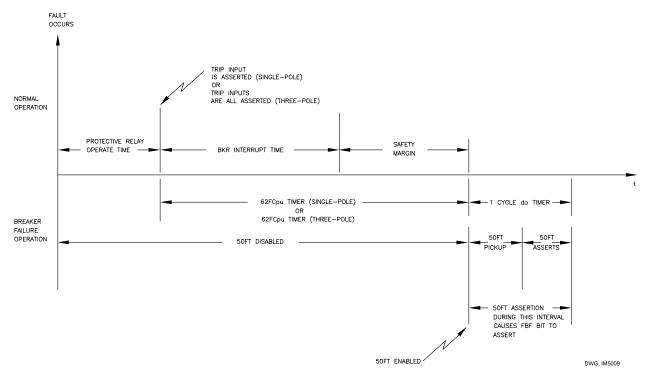

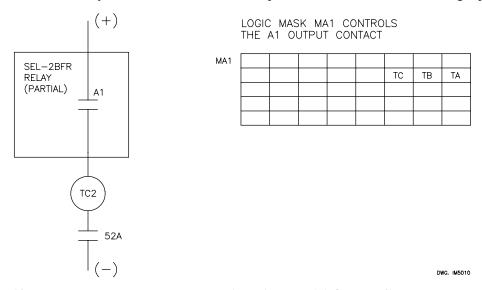

# **INSTRUCTION MANUAL**

# 20030207

SCHWEITZER ENGINEERING LABORATORIES 2350 NE HOPKINS COURT PULLMAN, WA USA 99163-5603 TEL: (509) 332-7890 FAX: (509) 332-7990

The software (firmware), schematic drawings, relay commands, and relay messages are copyright protected by the United States Copyright Law and International Treaty provisions. All rights are reserved.

You may not copy, alter, disassemble, or reverse-engineer the software. You may not provide the software to any third party.

All brand or product names appearing in this document are the trademark or registered trademark of their respective holders.

ACSELERATOR, Connectorized, conSELTANT, Job Done, Schweitzer Engineering Laboratories, SEL, SELogic, and SEL-PROFILE, are registered trademarks of Schweitzer Engineering Laboratories, Inc.

The English language manual is the only approved SEL manual.  $% \label{eq:english} % \label{english} % \lab$

$Copyright © @ SEL 1990, 1991, 1992, 1994, 1996, 1998, 1999, 2001, 2003 (All \ rights \ reserved) \ Printed \ in \ USA.$

This product is covered by U.S. Patent Numbers: 5,157,575 and 5,479,315.

This product is covered by the standard SEL 10-year warranty. For warranty details, visit www.selinc.com or contact your customer service representative.

PM2BFR-01

This device is shipped with default passwords. Default passwords should be changed to private passwords at installation. Failure to change each default password to a private password may allow unauthorized access. SEL shall not be responsible for any damage resulting from unauthorized access.

Cet équipement est expédié avec des mots de passe par défaut. A l'installation, les mots de passe par défaut devront être changés pour des mots de passe confidentiels. Dans le cas contraire, un accès non-autorisé à l'équipement pourrait être possible. SEL décline toute responsabilité pour tout dommage résultant de cet accès non-autorisé.

20001120

# MANUAL CHANGE INFORMATION

The date code at the bottom of each page of this manual reflects the creation or revision date. Date codes are changed only on pages that have been revised and any following pages affected by the revisions (i.e., pagination). If significant revisions are made to a section, the date code on all pages of the section will be changed to reflect the revision date.

Each time revisions are made, both the main table of contents and the affected individual section table of contents are regenerated and the date code is changed to reflect the revision date.

Changes in this manual to date are summarized below (most recent revisions listed at top).

| Revision<br>Date | Summary of Revisions                                                                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20030207         | Updated Appendix A: Firmware Versions in this Manual.                                                                                                                                                                     |

| 20010515         | Added information on the effect of 50FT pickup on IRIG-B operation in <b>Section 2: Specifications</b> and <b>Section 5: Applications</b> .                                                                               |

| 990714           | Changed footers on entire manual to reflect SEL-2BFR, -2/BFR.                                                                                                                                                             |

|                  | Added Model Variation Information to Section 1: Introduction.                                                                                                                                                             |

|                  | Incorporated SEL-2BFR-2 <i>Time Delayed Retrip</i> Logic into <i>Section 2: Specifications</i> .                                                                                                                          |

|                  | Modified AND and OR gate numbering in Section 2: Specifications.                                                                                                                                                          |

|                  | Reformatted Settings Sheets at end of Section 5: Event Reporting.                                                                                                                                                         |

|                  | Added <i>Appendix C: SEL-BFR</i> to explain SEL-BFR Relay differences.                                                                                                                                                    |

| 990512           | Clarified Figure 2.12 in Section 2: Specifications.                                                                                                                                                                       |

|                  | Updated Appendix A: Firmware Versions in this Manual.                                                                                                                                                                     |

| 981019           | Incorporated the following addenda into <i>Section 1: Introduction</i> : "ACB Phase Rotation Option" and "50 Hz Options."                                                                                                 |

|                  | Incorporated the following addenda into <i>Section 2: Specifications</i> : "New SEL-200 Series Optical Isolator Logic Input Rating" and "SEL-2BFR/BFR Instruction Manual Addendum for 1 Amp Version and 50/60 Hz Relays." |

|                  | Incorporated the following addendum into <b>Section 6: Installation</b> : "Jumper Installation Instructions."                                                                                                             |

|                  | Updated Figures 6.3, 6.4, and 6.5.                                                                                                                                                                                        |

| 970423           | 2BFR Specifications Addendum - Addition                                                                                                                                                                                   |

# SEL-2BFR, -2/BFR INSTRUCTION MANUAL TABLE OF CONTENTS

**SECTION 1: INTRODUCTION**

**SECTION 2: SPECIFICATIONS**

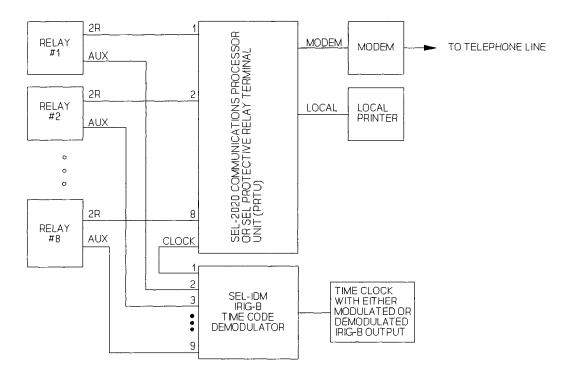

**SECTION 3: COMMUNICATIONS**

**SECTION 4: EVENT REPORTING**

**SECTION 5: APPLICATIONS**

**SECTION 6: INSTALLATION**

**SECTION 7: MAINTENANCE AND TESTING**

**SECTION 8: APPENDICES**

Date Code 20030207

**Appendix A: Firmware Versions in This Manual**

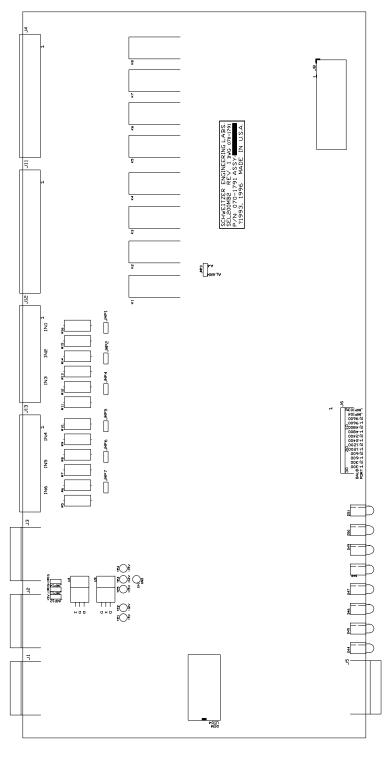

**Appendix B: Internal Diagrams**

**Appendix C: SEL-BFR Specifications**

# **TABLE OF CONTENTS**

| SECTION 1: I    | NTRODUCTION        | 1-1 |

|-----------------|--------------------|-----|

| Getting Started |                    | 1-1 |

| Overview        |                    | 1-1 |

| Relay Feat      | ures               | 1-1 |

|                 | ns                 |     |

|                 |                    |     |

| SEL-2BFR        | Relay              | 1-2 |

| 2BFR-2 Re       | elay               | 1-2 |

| Convention      | nal Terminal Block | 1-2 |

| Plug-In Co      | onnector           | 1-3 |

|                 | ation              |     |

| System Fre      | equency            | 1-3 |

|                 | otion              |     |

# **SECTION 1: INTRODUCTION**

## **GETTING STARTED**

This instruction manual applies to SEL-2BFR and SEL-2BFR-2 relays. *Appendix C: SEL-BFR Specifications* outlines the differences between the SEL-2BFR and legacy SEL-BFR relays. The hardware is identical for all SEL-2BFR relays.

If you are unfamiliar with the SEL-2BFR or SEL-2BFR-2 relays, we suggest that you read this section, then perform the Initial Checkout Procedure in *Section 7: Maintenance & Testing*. For a more detailed understanding of the relay, we suggest that you read the following sections in the outlined order:

**Section 2: Specifications** for a description of the logic and how it works with logic inputs, the Relay Word, and relay outputs

**Section 5: Applications** for a description of breaker failure timing, an application outline that guides settings selection, and Settings Sheets.

**Section 3: Communications** for a description of the commands used to set the relay for protection, set the relay for control, obtain target information, obtain metering information, etc.

**Section 4: Event Reporting** for a description of event report generation, summary event reports, long event reports, and their interpretation.

#### **OVERVIEW**

#### **Relay Features**

The SEL-2BFR Breaker Failure Relay and Monitor performs many circuit breaker protective relaying, diagnostic, and data recording functions. The relay detects the following line circuit breaker failure modes:

- Failure to clear a fault (six available schemes).

- Failure to trip under load.

- Failure of the breaker auxiliary contact to indicate that the breaker tripped.

- Failure to complete trip sequence due to trip resistor(s) remaining inserted.

- Failure to complete close sequence due to close resistor(s) remaining inserted.

- Failure to close.

- Failure while open: breaker pole flashover detected.

Other features and capabilities include:

- Recording of summaries for the last 100 breaker operations.

- Fifteen-cycle event recording of the last nine operations.

- Alarm event history including slow trip, slow close, blown potential fuse, etc.

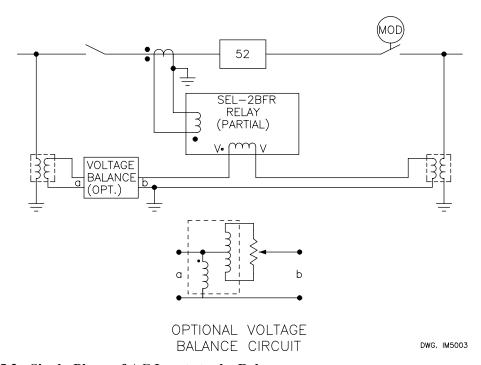

- Motor-Operated Disconnect (MOD) trip and power circuit breaker isolation security logic.

- Instantaneous or time-delayed retripping capability.

- User-selectable targets for operations and testing.

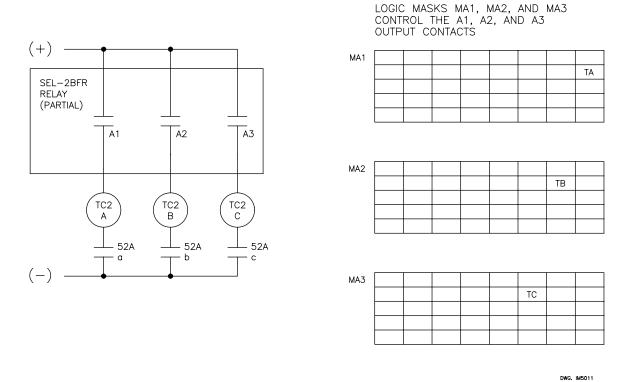

- Programmable Mask Logic for flexible application and testing.

- Metering.

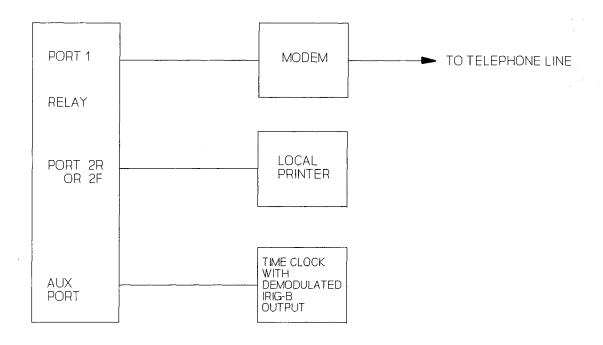

- Communications ports for local and remote access.

- Automatic self-tests.

- Demodulated IRIG-B time code input port.

- Compact size.

Unique protection features and economy make the SEL-2BFR Relay an ideal breaker failure relay.

# **MODEL VARIATIONS**

# SEL-BFR

This manual is written for SEL-2BFR relays. For SEL-BFR relays, substitute SEL-BFR for each reference to SEL-2BFR. Refer to . *Appendix C: SEL-BFR Specifications* for SEL-BFR general specifications and drawings

#### SEL-2BFR Relay

The basic SEL-2BFR relay has all the features outlined in the preceding Overview.

#### 2BFR-2 Relay

This variation adds a timer, RTSD (Retrip Seal-In Delay), to delay the seal-in of the trip input in the time-delayed retrip logic. This timer has a settable pickup time and instantaneous dropout time. You can set the pickup time to filter out undesirable transients, see *Section 2: Specifications*.

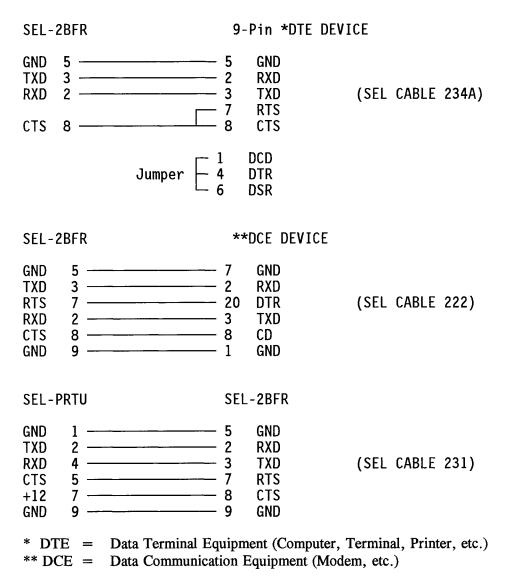

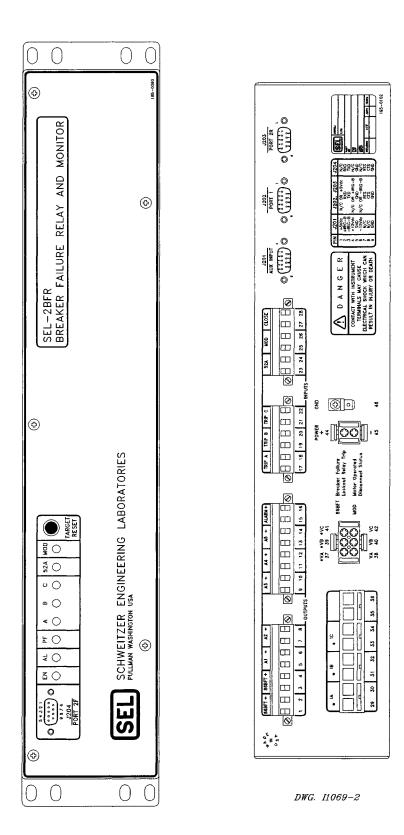

#### **Conventional Terminal Block**

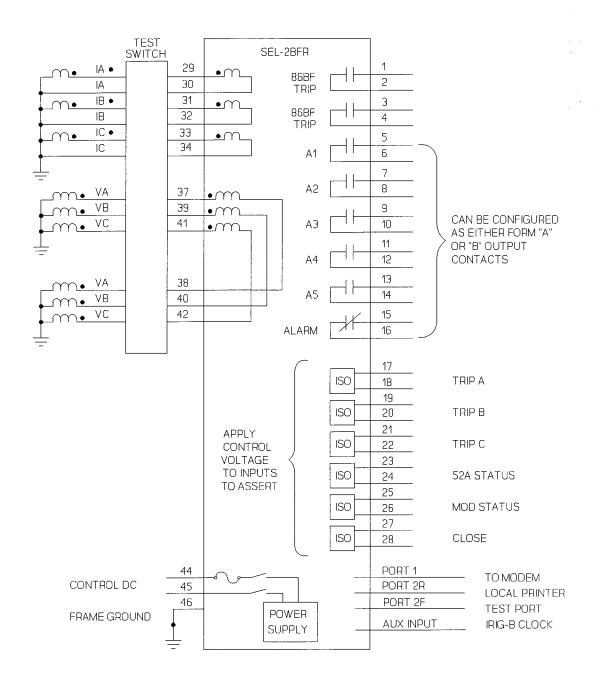

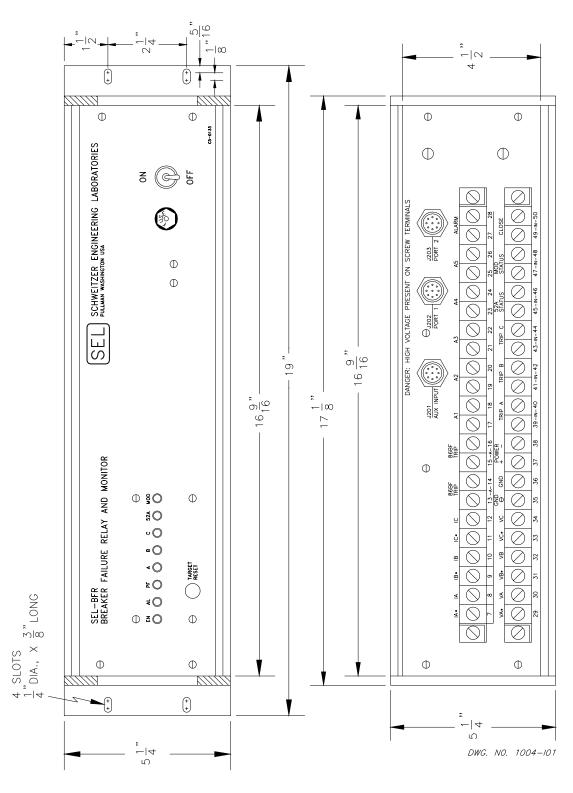

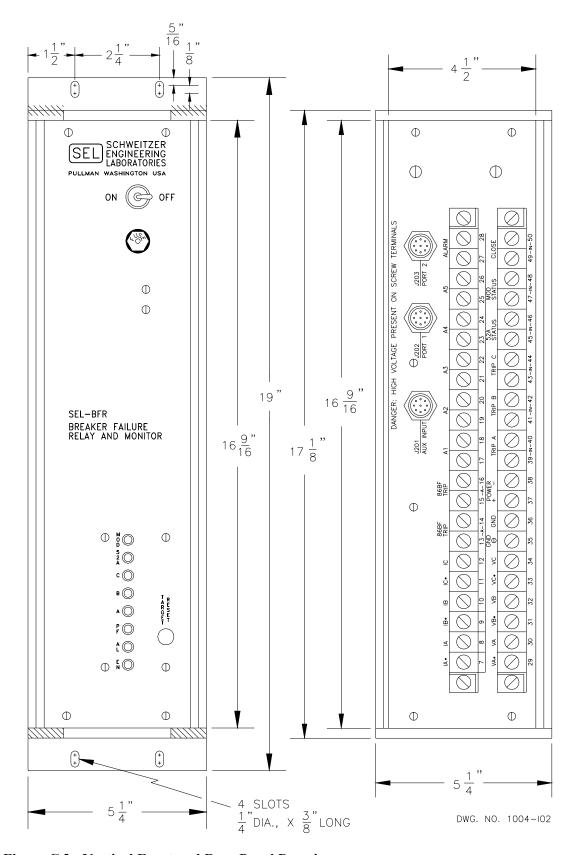

This model includes hardware that supports three current inputs, three voltage inputs, six optoisolated inputs, eight output contacts, two EIA-232 ports, and IRIG-B time code in a 3.5" (2U) rack mount package. It uses terminal blocks that support #6 ring terminals. This robust package meets or exceeds numerous industry standard type tests.

# **Plug-In Connector**

This model includes hardware that supports all of the features of the conventional terminal block model. It differs in its use of plug-in connectors instead of terminal blocks. In addition, it provides

- High current interrupting output contacts.

- Ouick connect/release hardware for rear-panel terminals.

- Time code input access on all rear communications ports.

This robust package meets or exceeds numerous industry standard type tests.

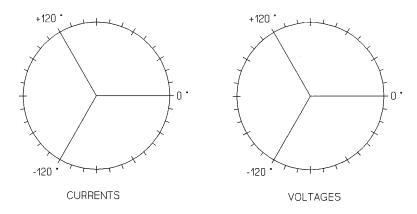

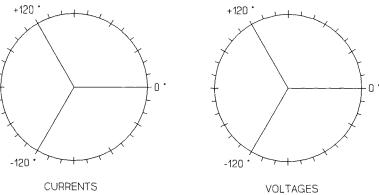

# **Phase Rotation**

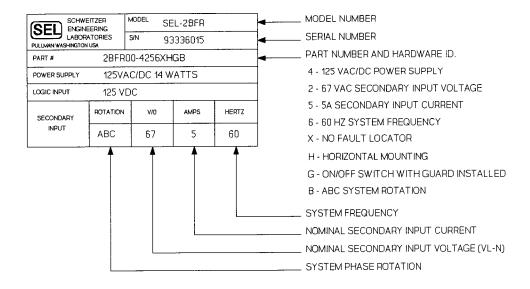

This manual is written for standard ABC phase rotation applications. If your SEL relay is ordered with the ACB phase rotation option, references made in the instruction manual to voltage and current phase angle should be noted accordingly. The firmware identification number (FID) may be used to verify whether your relay was ordered with ABC ("B") or ACB ("C") rotation.

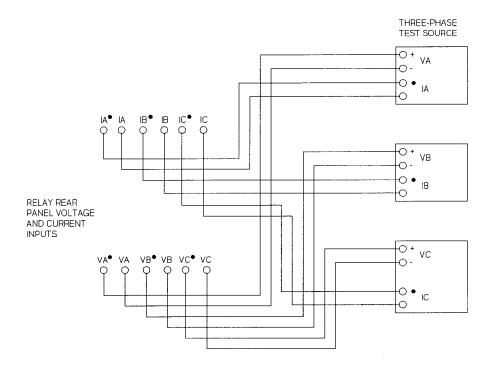

All current and voltage inputs are connected to the SEL relay rear panel as shown in the instruction manual.

# **System Frequency**

This manual is written for relays operating at a nominal system frequency of 60 Hz. For relays which specify a nominal frequency of 50 Hz, substitute 50 Hz for each reference to 60 Hz.

References made to a sampling time of 1/240 seconds should be replaced with a time of 1/200 seconds.

#### **GENERAL DESCRIPTION**

The SEL-2BFR Relay is a single- or three-pole breaker failure protection and monitoring package. The relay provides classical overcurrent-based breaker failure protection for a wide variety of breaker arrangements. Additional features include metering, event reporting, remote setting capabilities, breaker operating time monitors, energy interruption monitors, and breaker resistor thermal protection. Simple hardware design and efficient digital signal processing ensure reliability. Extensive self-testing and communication capabilities enhance availability.

The SEL-2BFR Relay has six fault current-driven breaker protection schemes, including one specially designed for ring-bus or breaker-and-a-half applications. Tailor the relay to your circuit breaker protection requirements by selecting the most appropriate scheme.

The relay detects failures to interrupt fault, load, or line-charging current. It also detects failures of breaker poles to complete a close sequence. When potential transformers are used, the relay can detect open breaker pole flashover failures.

Independent phase current detectors, protection logic, and timers make the relay easy to apply on both simple systems and more complicated breaker arrangements such as single-pole trip installations.

The SEL-2BFR Relay stores summaries of the 100 latest events in nonvolatile memory. These summaries include event type, mechanical and electrical operating times, breaker energy, and date and time of operation. Using this breaker history, you can monitor breaker wear and effectively schedule routine breaker maintenance.

A breaker can occasionally operate incompletely, leaving trip or close resistors in service. The energy dissipated in a breaker resistor due to current flow can exceed the resistor thermal rating within seconds, resulting in dangerous and expensive resistor failure.

When potential transformer inputs are used, the SEL-2BFR Relay uses six thermal models to monitor energy dissipated in breaker trip and close resistors. When a resistor temperature estimate reaches preset limits, the relay can alarm, generate an event report, or trip the lockout relay. Resistor thermal models have pending failure and failure temperature levels.

The thermal protection function does not require an initiating input; it monitors the breaker continuously. Thermal protection can be disabled when trip and close resistors are not used.

When you use a single motor-operated disconnect switch (MOD) with the protected breaker, the SEL-2BFR Relay can trip the MOD to isolate the failed breaker when phase current drops below a settable value. When an MOD is not installed, the MOD logic may be used to indicate a 'Safe to Disconnect' condition to personnel.

The relay also includes Programmable Mask Logic, which allows you to configure the 86BF TRIP and five auxiliary outputs to operate when any of 40 protective elements or logic outputs pick up. You can implement complete application-specific protective schemes with a minimum of wiring and panel space. Programmable Mask Logic also simplifies relay testing.

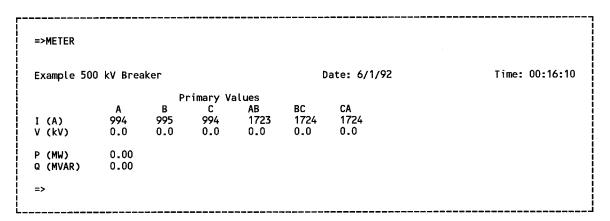

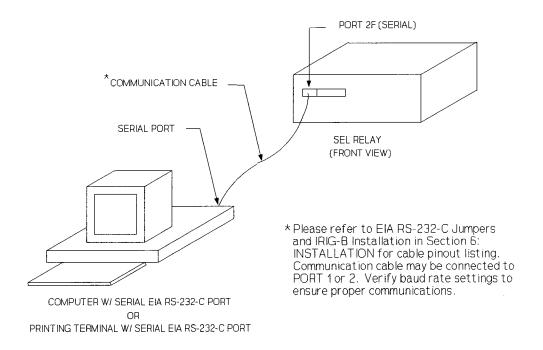

Communications functions provide remote and local examination of a wide range of data, including the voltages and currents presented to the instrument, relay settings, and a history of the last 100 events. You can enter and modify relay settings remotely; you can also control all outputs via the communications channel. A two-level password scheme protects settings and circuit breaker control. The SEL-2BFR Relay monitors password execution and closes the ALARM contact output to indicate possible unauthorized access. The relay requires no special communication software. Access the relay with a dumb terminal, printing terminal, or computer with serial port and terminal emulation software.

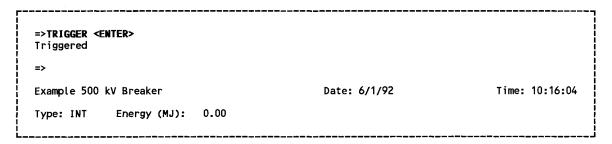

A wide range of user-selectable events, including any input or output assertion (except ALARM), triggers the event record function. Assertion of the 86BF TRIP output automatically generates an event report. You can also set the relay to trigger an event report for CLOSE or TRIP input assertions. This ensures a record of every normal circuit breaker operation, as well as every circuit breaker failure (*Section 4: Event Reporting* includes more details on triggering event reports).

The event report contains all information needed to determine the cause of relay and breaker operations. These 15-cycle reports contain current, voltage, input, output, and relay element data presented on a quarter-cycle basis. Parameters such as event type, relay response time, circuit breaker operation time, currents, voltages, and breaker power dissipation appear directly in the

event report or can be calculated from the data stored. All event reports are time-tagged by a self-contained clock/calendar.

The SEL-2BFR Relay is available in either a conventional terminal block or plug-in connector model. The conventional terminal block relay has #6-32 screw terminals for ring lugs. The plug-in connector model offers easy and fast connector installation and replacement through the use of plug-in connectors. Inputs and outputs use Euro-style plugs. CT, PT, and power connectors come with factory-crimped custom wiring harnesses. Shorting mechanisms within CT plugs automatically short CT secondaries upon removal of the plugs from the relay.

High current interrupting contacts are standard on the SEL-2BFR plug-in connector model. These contacts use an electromechanical relay with solid state circuitry to interrupt dc currents far greater than that of a typical contact output. This circuitry employs no silicon-controlled rectifiers (SCRs). The circuit is designed to make 30 Adc, carry 6 Adc, and interrupt 10 Adc. The circuit can interrupt 10 Adc four times in one second. The circuit then must cool for two minutes to prevent thermal damage.

# **TABLE OF CONTENTS**

| SECTI | ON 2: SPECIFICATIONS                                       | 2-1 |

|-------|------------------------------------------------------------|-----|

| G     | eneral Specifications                                      | 2-1 |

|       | General                                                    |     |

|       | Fault Current Element (50FT)                               |     |

|       | MOD Current Element (50MD)                                 |     |

|       | Load/Line-Charging Current Element (50LD)                  |     |

|       | Flashover Voltage Element (59FO)                           |     |

|       | Negative-Sequence Overvoltage Element (47Q)                |     |

|       | Flashover Voltage Element (59H)                            | 2-4 |

|       | Voltage Across Closed Breaker Element (Vwarn)              |     |

|       | Current Unbalance Element (87UB)                           |     |

|       | Overpower Elements (37OP)                                  |     |

|       | Breaker Resistor Thermal Elements (26CF, 26CP, 26TF, 26TP) |     |

|       | Settable Timers                                            |     |

| т.    | Fixed Timers                                               |     |

|       | ogic Inputs                                                |     |

| R     | elay Outputs                                               |     |

|       | 86BF TRIP Output                                           |     |

|       | Programmable Outputs (A1, A2, A3, A4, A5)                  |     |

| D     | ALARM Output                                               |     |

|       | elay Word                                                  |     |

|       | rogrammable Output Logic                                   |     |

|       | elay Targets                                               |     |

|       | ignal Processing                                           |     |

| L     | ogic Description                                           |     |

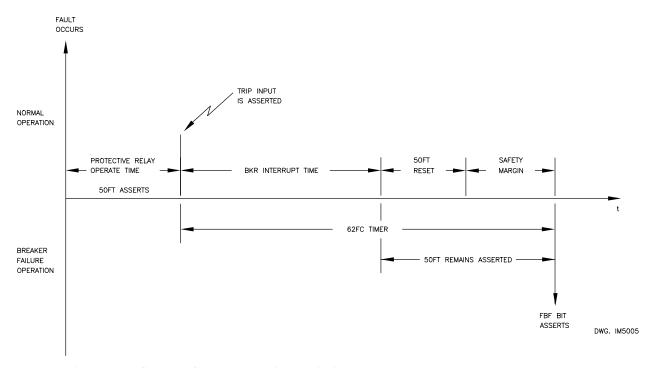

|       | Scheme 1                                                   |     |

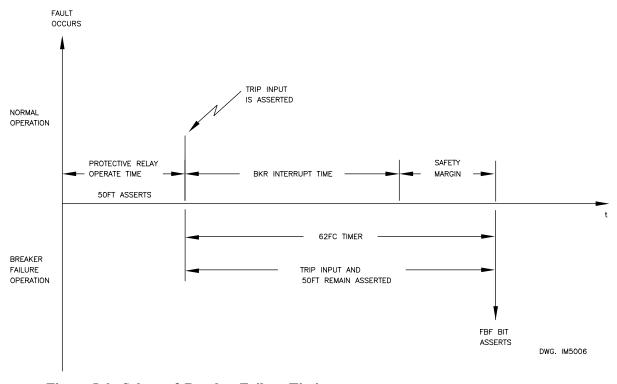

|       | Scheme 2                                                   |     |

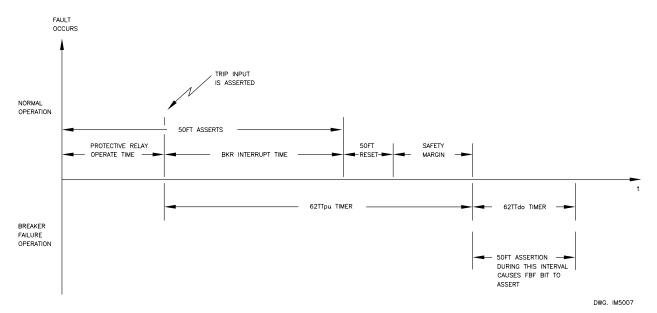

|       | Scheme 3                                                   |     |

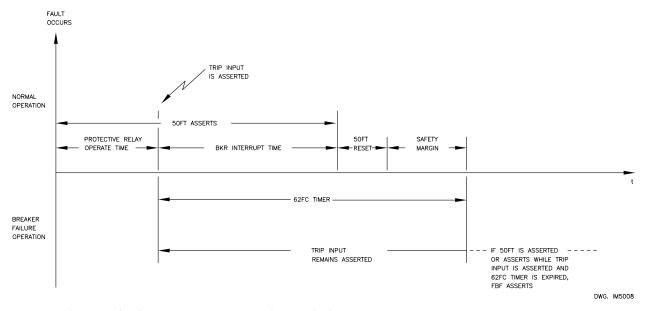

|       | Scheme 4                                                   |     |

|       | Scheme 5                                                   |     |

|       | Scheme 6                                                   |     |

|       | Protection While Tripping Load or Line-Charging Current    |     |

|       | Thermal Protection of Close and Trip Resistors             |     |

|       | Protection for Current Through an Open Breaker (Flashover) |     |

|       | Protection for Failure to Close                            |     |

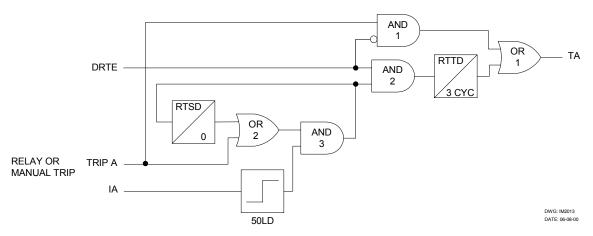

|       | Time-Delayed Breaker Retrip (SEL-2BFR Relay)               |     |

|       | Time-Delayed Breaker Retrip (SEL-2BFR-2 Relay)             |     |

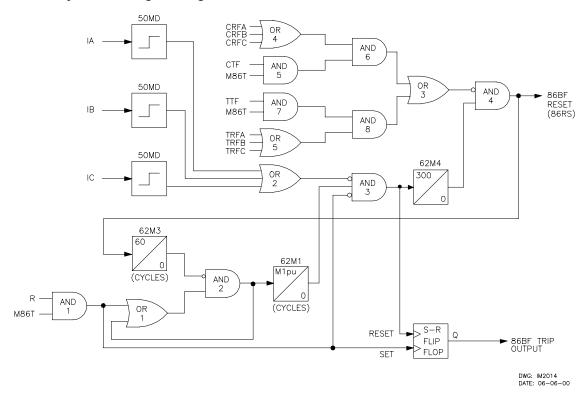

|       | 86BF Trip and Reset Logic                                  |     |

|       | MOD Trip Disabled                                          |     |

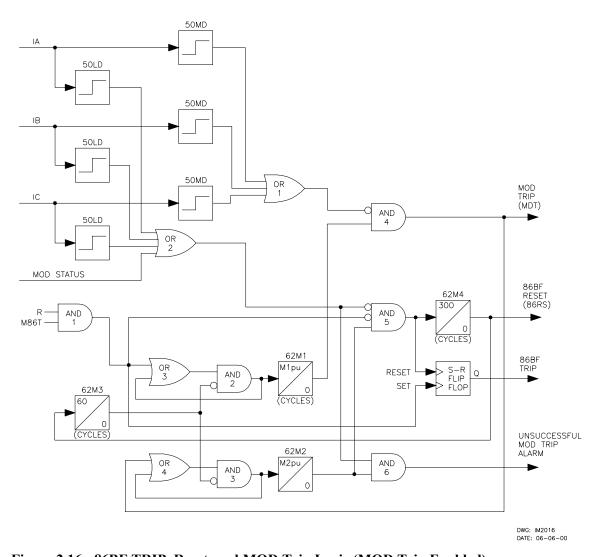

|       | MOD Trip Enabled                                           |     |

|       | 52BV Logic                                                 |     |

|       | Alarm Logic                                                |     |

|       | Failed CB Trip Resistors Put in Service                    |     |

|       | Failed CB Close Resistors Put in Service                   |     |

|       | 52A Contradicts Voltage                                    |     |

|       | 5                                                          |     |

|                                                                                                                                                                                                 | Current While Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-29                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                                                                                                                                                                                 | Trip While Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

|                                                                                                                                                                                                 | CB Did Not Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    |

|                                                                                                                                                                                                 | Blown Pot Fuse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

|                                                                                                                                                                                                 | Current After MOD Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |

|                                                                                                                                                                                                 | MOD Contradicts Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |

|                                                                                                                                                                                                 | MOD Trip Failed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

|                                                                                                                                                                                                 | Volts Across Closed CB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |

|                                                                                                                                                                                                 | Slow Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-30                                                                               |

|                                                                                                                                                                                                 | Slow Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

| Seri                                                                                                                                                                                            | al Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-31                                                                               |

| IRI                                                                                                                                                                                             | G-B Input Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-31                                                                               |

|                                                                                                                                                                                                 | nt Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                    |

|                                                                                                                                                                                                 | ering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

|                                                                                                                                                                                                 | -Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

|                                                                                                                                                                                                 | Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |

|                                                                                                                                                                                                 | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-33                                                                               |

|                                                                                                                                                                                                 | Random-Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                    |

|                                                                                                                                                                                                 | Read-Only Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    |

|                                                                                                                                                                                                 | Analog-to-Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                    |

|                                                                                                                                                                                                 | Master Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |

|                                                                                                                                                                                                 | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

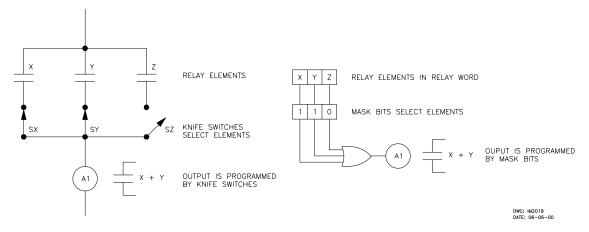

| Pro                                                                                                                                                                                             | grammable Logic Mask Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                    |

|                                                                                                                                                                                                 | rcurrent Element Operating Time Curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |

|                                                                                                                                                                                                 | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                    |

|                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

| Table 2.1:                                                                                                                                                                                      | Logic Input Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-6                                                                                |

| Table 2.1:<br>Table 2.2:                                                                                                                                                                        | Logic Input Functions SEL-2BFR Relay Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

|                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-7                                                                                |

| Table 2.2:                                                                                                                                                                                      | SEL-2BFR Relay Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7                                                                                |

| Table 2.2:<br>Table 2.3:                                                                                                                                                                        | SEL-2BFR Relay Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10                                                                 |

| Table 2.2:<br>Table 2.3:<br>Table 2.4:                                                                                                                                                          | SEL-2BFR Relay Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10                                                                 |

| Table 2.2:<br>Table 2.3:<br>Table 2.4:                                                                                                                                                          | SEL-2BFR Relay Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10                                                                 |

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:                                                                                                                                            | SEL-2BFR Relay Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10<br>2-33                                                         |

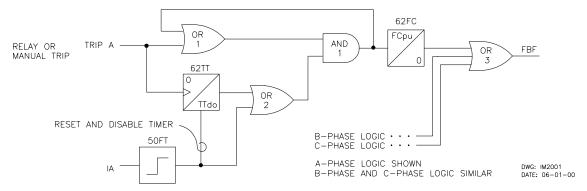

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:                                                                                                                                            | SEL-2BFR Relay Word Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10<br>2-33                                                         |

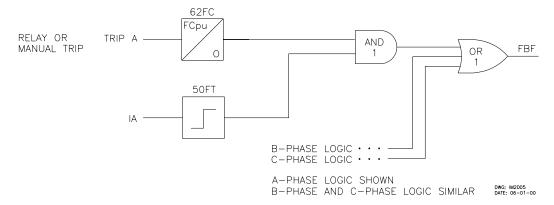

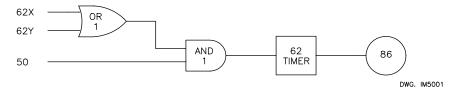

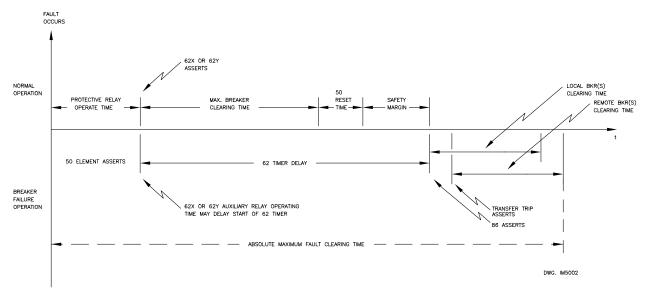

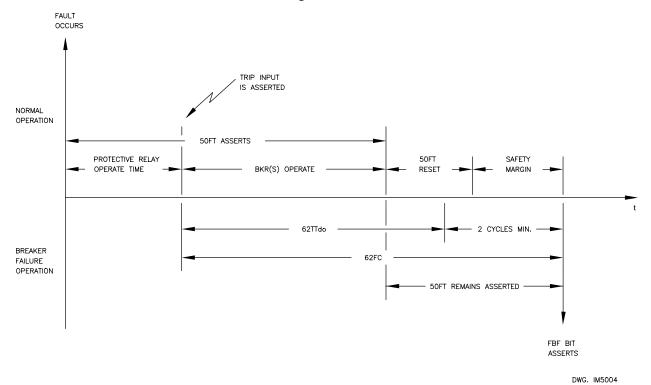

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.2:                                                                                                              | SEL-2BFR Relay Word Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-7<br>2-8<br>2-10<br>2-33                                                         |

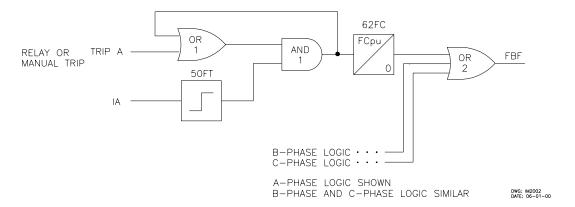

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.2:<br>Figure 2.3:                                                                                               | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10<br>2-33<br>2-13<br>2-13<br>2-14                                 |

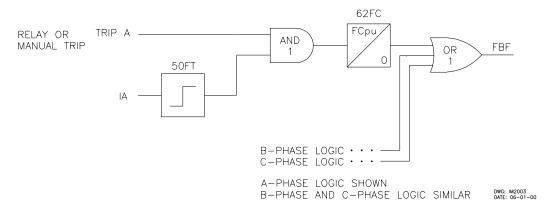

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.2:<br>Figure 2.3:<br>Figure 2.4:                                                                                | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-7<br>2-8<br>2-10<br>2-33<br>2-13<br>2-13<br>2-14<br>2-14                         |

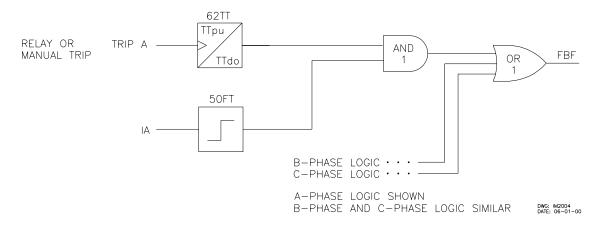

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.2:<br>Figure 2.3:<br>Figure 2.4:<br>Figure 2.5:                                                                 | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5                                                                                                                                                                                                                                                                                                                                                                                                | 2-7<br>2-8<br>2-10<br>2-33<br>2-13<br>2-14<br>2-14<br>2-15                         |

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.2:<br>Figure 2.3:<br>Figure 2.4:<br>Figure 2.5:<br>Figure 2.6:                                                  | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase and Three-Phase Failure to Trip for Fault Logic, Scheme 6                                                                                                                                                                                                                                                                            | 2-7<br>2-8<br>2-10<br>2-33<br>2-13<br>2-14<br>2-14<br>2-15<br>2-15                 |

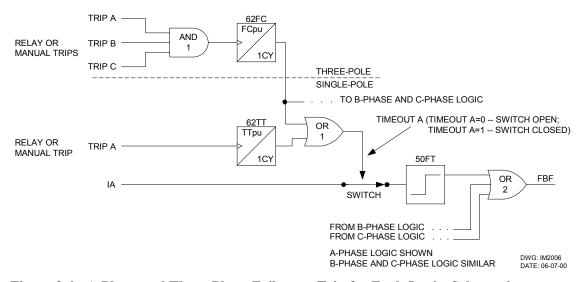

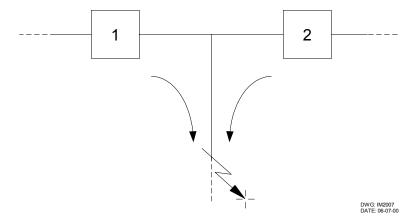

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.2:<br>Figure 2.3:<br>Figure 2.4:<br>Figure 2.5:<br>Figure 2.6:<br>Figure 2.7:                                   | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 Double-Breaker Arrangement Provides Two Fault Current Sources                                                                                                                                                                                                                                                                                | 2-7<br>2-8<br>2-10<br>2-33<br>2-13<br>2-14<br>2-14<br>2-15<br>2-15<br>2-17         |

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.3:<br>Figure 2.4:<br>Figure 2.5:<br>Figure 2.6:<br>Figure 2.7:<br>Figure 2.8:                                   | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase and Three-Phase Failure to Trip for Fault Logic, Scheme 6 Double-Breaker Arrangement Provides Two Fault Current Sources Failure to Trip Load or Line-Charging Current Logic                                                                                                        | 2-7<br>2-8<br>2-10<br>2-33<br>2-13<br>2-14<br>2-14<br>2-15<br>2-15<br>2-17<br>2-18 |

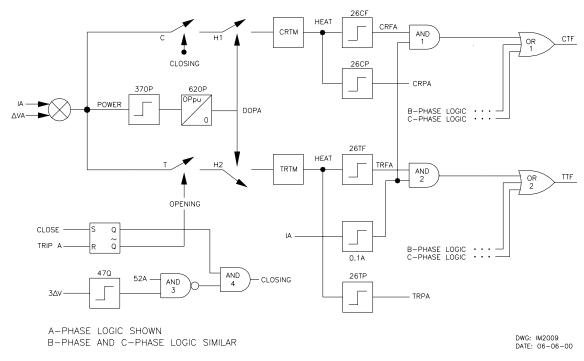

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.3:<br>Figure 2.4:<br>Figure 2.5:<br>Figure 2.6:<br>Figure 2.7:<br>Figure 2.8:<br>Figure 2.9:                    | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 6 Double-Breaker Arrangement Provides Two Fault Current Sources Failure to Trip Load or Line-Charging Current Logic Trip and Close Resistor Thermal Protection Logic                                                                                                                         | 2-7 2-8 2-10 2-33 2-13 2-14 2-14 2-15 2-15 2-17 2-18 2-20                          |

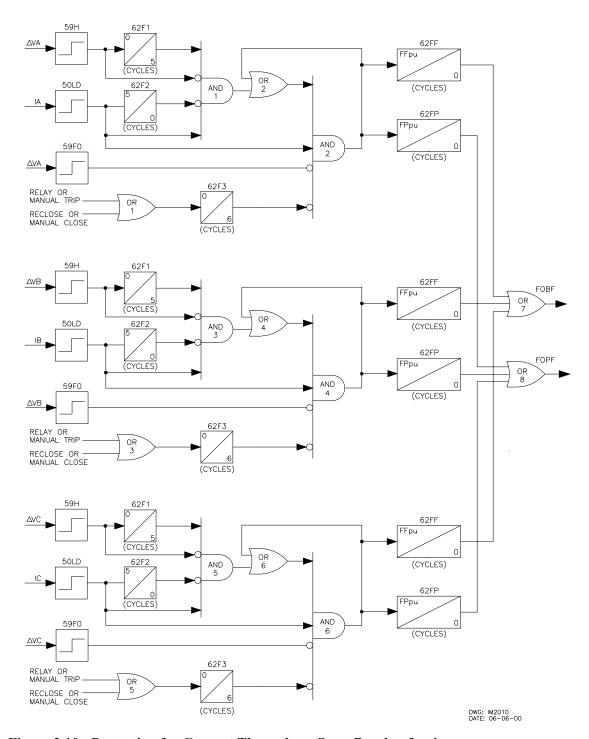

| Table 2.2:<br>Table 2.3:<br>Table 2.4:<br>Table 2.5:<br>Figure 2.1:<br>Figure 2.3:<br>Figure 2.4:<br>Figure 2.6:<br>Figure 2.7:<br>Figure 2.8:<br>Figure 2.9:<br>Figure 2.10:                   | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 Ta-Phase and Three-Phase Failure to Trip for Fault Logic, Scheme 6 Double-Breaker Arrangement Provides Two Fault Current Sources Failure to Trip Load or Line-Charging Current Logic Trip and Close Resistor Thermal Protection Logic Protection for Current Through an Open Breaker Logic | 2-7 2-8 2-10 2-13 2-13 2-14 2-14 2-15 2-15 2-17 2-18 2-20 2-21                     |

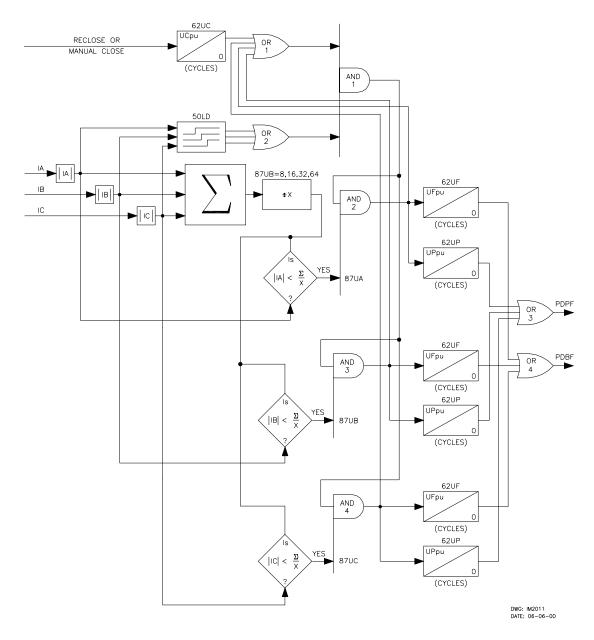

| Table 2.2: Table 2.3: Table 2.4: Table 2.5: Figure 2.1: Figure 2.2: Figure 2.4: Figure 2.5: Figure 2.6: Figure 2.7: Figure 2.8: Figure 2.9: Figure 2.10: Figure 2.11:                           | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase and Three-Phase Failure to Trip for Fault Logic, Scheme 6 Double-Breaker Arrangement Provides Two Fault Current Sources Failure to Trip Load or Line-Charging Current Logic Trip and Close Resistor Thermal Protection Logic Protection for Current Through an Open Breaker Logic Phase Discordance While Closing Logic              | 2-7 2-8 2-10 2-13 2-13 2-14 2-14 2-15 2-15 2-17 2-18 2-20 2-21 2-23                |

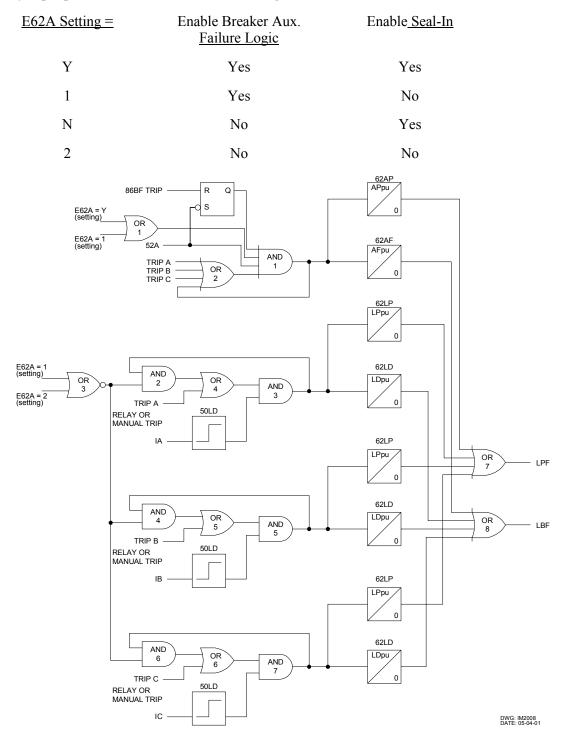

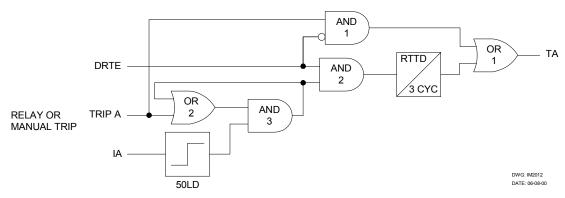

| Table 2.2: Table 2.3: Table 2.4: Table 2.5: Figure 2.1: Figure 2.2: Figure 2.4: Figure 2.5: Figure 2.6: Figure 2.7: Figure 2.8: Figure 2.9: Figure 2.10: Figure 2.11: Figure 2.11: Figure 2.12: | Relay Word Bit Definitions Front-Panel Target Illumination Conditions Power Supply Self-Test Limits  FIGURES  A-Phase Failure to Trip for Fault Logic, Scheme 1 A-Phase Failure to Trip for Fault Logic, Scheme 2 A-Phase Failure to Trip for Fault Logic, Scheme 3 A-Phase Failure to Trip for Fault Logic, Scheme 4 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 A-Phase Failure to Trip for Fault Logic, Scheme 5 Ta-Phase and Three-Phase Failure to Trip for Fault Logic, Scheme 6 Double-Breaker Arrangement Provides Two Fault Current Sources Failure to Trip Load or Line-Charging Current Logic Trip and Close Resistor Thermal Protection Logic Protection for Current Through an Open Breaker Logic | 2-7 2-8 2-10 2-33 2-13 2-13 2-14 2-15 2-15 2-17 2-18 2-20 2-21 2-23 2-24           |

| Figure 2.14: | 86BF TRIP and Reset Logic (MOD Trip Disabled)           | 2-25 |

|--------------|---------------------------------------------------------|------|

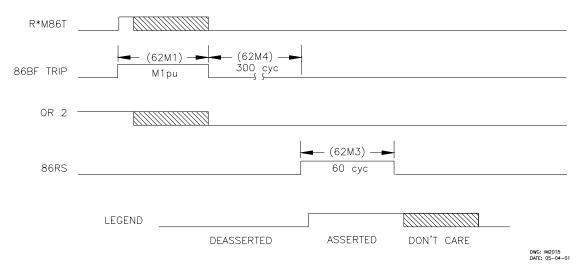

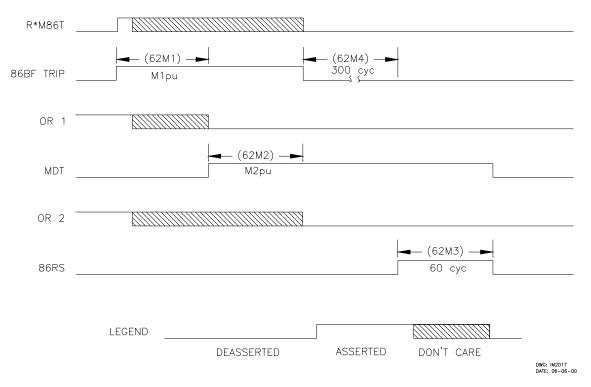

| Figure 2.15: | MOD Trip Disabled Logic Timing Diagram                  | 2-26 |

|              | 86BF TRIP, Reset, and MOD Trip Logic (MOD Trip Enabled) |      |

| Figure 2.17: | MOD Trip Enabled Logic Timing Diagram                   | 2-28 |

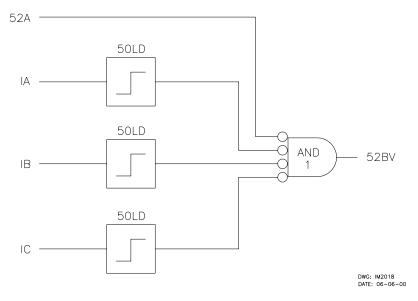

| Figure 2.18: | 52BV Logic                                              | 2-28 |

| Figure 2.19: | Programmable Logic Mask Analogy                         | 2-35 |

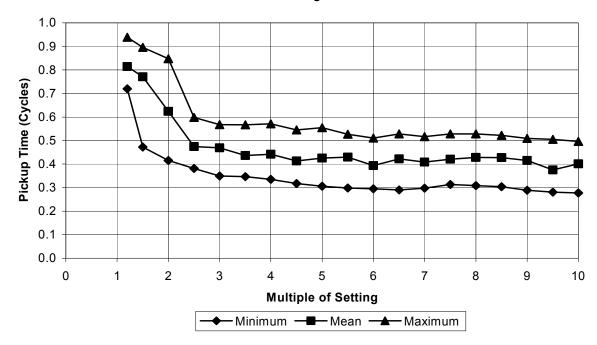

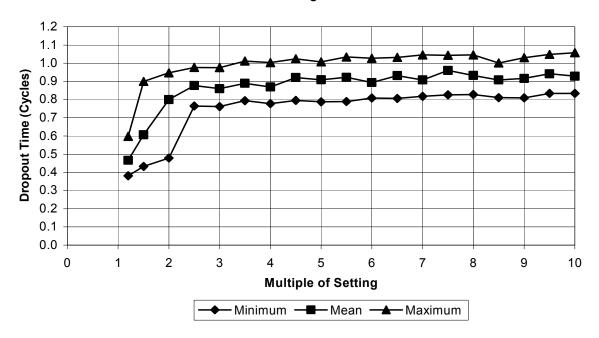

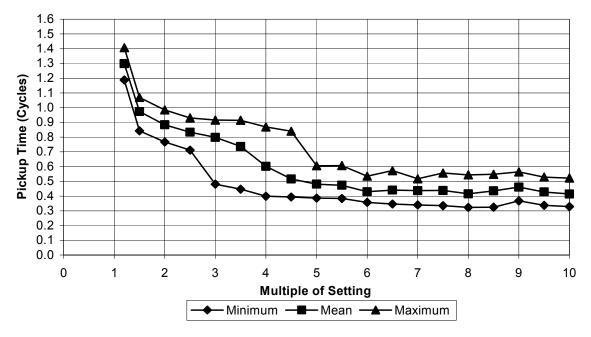

| Figure 2.20: | 50FT Pickup Time Curves                                 | 2-36 |

| Figure 2.21: | 50FT Dropout Time Curves                                | 2-36 |

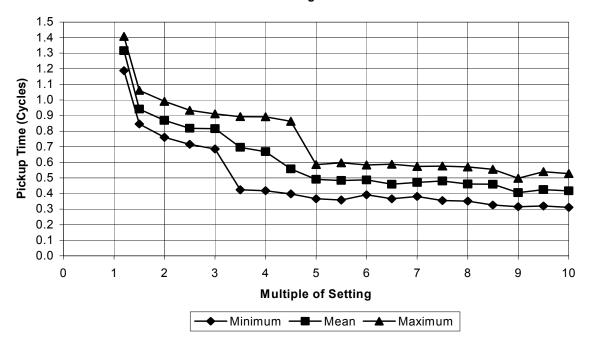

| Figure 2.22: | 50MD Pickup Time Curves                                 | 2-37 |

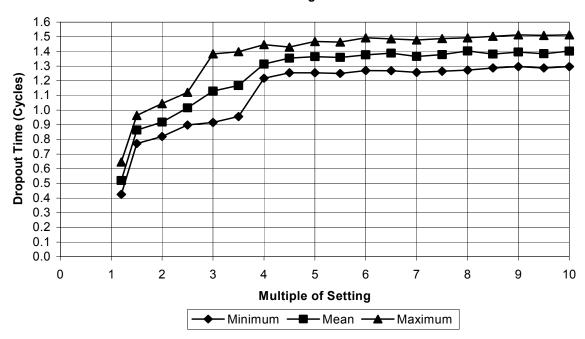

| Figure 2.23: | 50MD Dropout Time Curves                                | 2-37 |

| Figure 2.24: | 50LD Pickup Time Curves                                 | 2-38 |

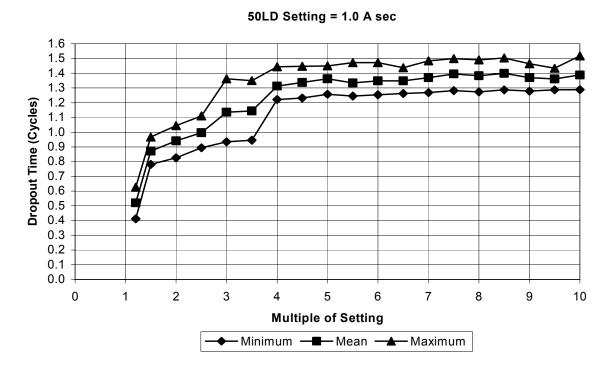

| Figure 2.25: | 50LD Dropout Time Curves                                | 2-38 |

# **SECTION 2: SPECIFICATIONS**

## **GENERAL SPECIFICATIONS**

# General

Tightening Torque: Terminal Block:

Minimum: 7-in-lb (0.8 Nm) Maximum: 12-in-lb (1.4 Nm)

Connectorized®:

Minimum: 4.4-in-lb (0.5 Nm) Maximum: 8.8-in-lb (1.0 Nm)

**Terminal** Terminals or stranded copper wire. Ring terminals are recommended. Minimum temperature rating

**Connections:** of 105°C.

AC Current Inputs: 5 A nominal: 15 A continuous, 500 A for 1 s, linear to 155 A symmetrical.

1250 A for 1 cycle.

Burden: 0.27 VA at 5 A, 2.51 VA at 15 A.

1 A nominal: 3 A continuous, 100 A for 1 s, linear to 31 A symmetrical.

250 A for 1 cycle.

Burden: 0.06 VA at 1 A, 0.5 VA at 3 A.

AC Voltage Inputs: 150 V<sub>L-N</sub>, three-phase, four-wire connection.

150 V continuous (connect any voltage from 0 to 150 Vac).

365 V for 10 s.

Burden: 0.07 VA @ 67 V; 0.42 VA @ 150 V.

**Power Supply:** Rated: 125/250 Vdc:

Range: 85–350 Vdc or 85–264 Vac

Burden: <15 W

Interruption: 30 ms @125 Vdc

Ripple: 100%

Rated: 24/48 Vdc:

Range: 20–60 Vdc

Burden: <15 W

Interruption: 30 ms @ 48 Vdc

Ripple: 5%

Note: Interruption and Ripple per IEC 255-11: 1979.

Output Contacts: Standard (Terminal Block Option):

Make: 30 A; Carry: 6 A continuous carry at 70°C; 1 s Rating: 50 A; MOV protected: 270 Vac,

360 Vdc, 40 J;

Pickup time: Less than 5 ms. Dropout time: Less than 5 ms, typical.

Breaking Capacity (10000 operations):

24 V 0.75 A L/R = 40 ms 48 V 0.50 A L/R = 40 ms 125 V 0.30 A L/R = 40 ms 250 V 0.20 A L/R = 40 ms

Cyclic Capacity (2.5 cycles/second):

24 V 0.75 A L/R = 40 ms 48 V 0.50 A L/R = 40 ms 125 V 0.30 A L/R = 40 ms 250 V 0.20 A L/R = 40 ms

High Current Interrupting (Connectorized Option):

Make: 30 A; Carry: 6 A continuous carry at 70°C; 1 s Rating: 50 A;

MOV protected: 330 Vdc, 40 J;

Pickup time: Less than 5 ms; Dropout time: Less than 8 ms, typical.

Breaking Capacity (10000 operations):

24 V 10 A L/R = 40 ms48 V 10 A L/R = 40 ms125 V 10 A L/R = 40 ms250 V 10 A L/R = 20 ms

Cyclic Capacity (4 cycles in 1 second, followed by 2 minutes idle for thermal dissipation):

24 V 10 A L/R = 40 ms48 V 10 A L/R = 40 ms125 V 10 A L/R = 40 ms250 V 10 A L/R = 20 ms

Note: Do not use high current interrupting output contacts to switch ac control signals. These outputs

are polarity dependent.

Note: Make per IEEE C37.90: 1989; Breaking and Cyclic Capacity per IEC 255-23: 1994.

Optoisolated Inputs: 250 Vdc: Pickup 150-300 Vdc.

125 Vdc: Pickup 100-150 Vdc; Dropout 75 Vdc (Connectorized Option).

48 Vdc: Pickup 30–60 Vdc; (Terminal Block Option).

48 Vdc: Pickup 38.4-60 Vdc; Dropout 28.8 Vdc (Connectorized Option).

24 Vdc: Pickup 15.0-30 Vdc.

Note: Terminal Block Option: 24, 48, and 250 Vdc optoisolated inputs draw approximately 4 mA of current, and 125 Vdc inputs draw approximately 6 mA of current. Connectorized Option: 24 and 250 Vdc optoisolated inputs draw approximately 4 mA of current, 48 Vdc inputs draw approximately 5 mA of current, and 125 Vdc inputs draw approximately 6 mA of current. All current ratings are at nominal input voltage.

Routine

AC current inputs, AC voltage inputs: 2500 Vac for 10 s; power supply, optoisolated inputs,

**Dielectric Strength:**

and output contacts: 3100 Vdc for 10 s.

Frequency and Rotation

System Frequency: 50 or 60 Hz are ordering options; Phase Rotation: ABC or ACB are ordering options.

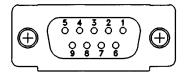

Communications

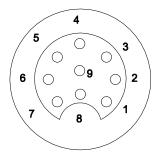

EIA-232: Baud rate: 300-9600 baud; includes front and rear connector for Port 2. Ports:

**Time-Code Input:** Relay accepts demodulated IRIG-B time-code input at AUX INPUT.

**Operating Temp.:**  $-40^{\circ}$  to  $+70^{\circ}$ C ( $-40^{\circ}$  to  $+158^{\circ}$ F).

Weight: 12 lbs (5.5 kg).

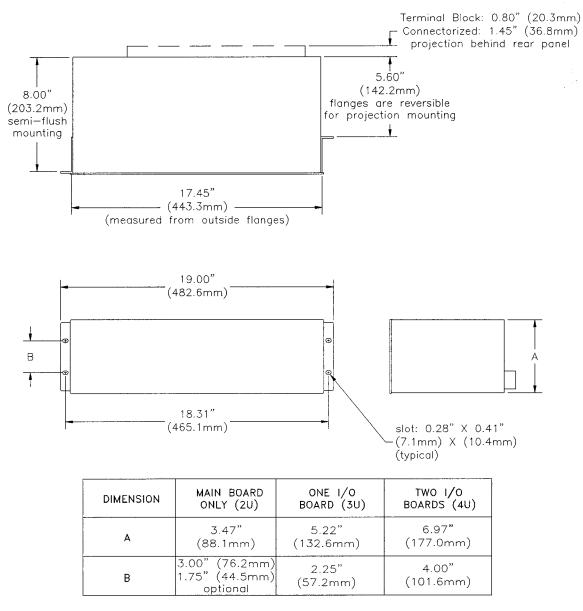

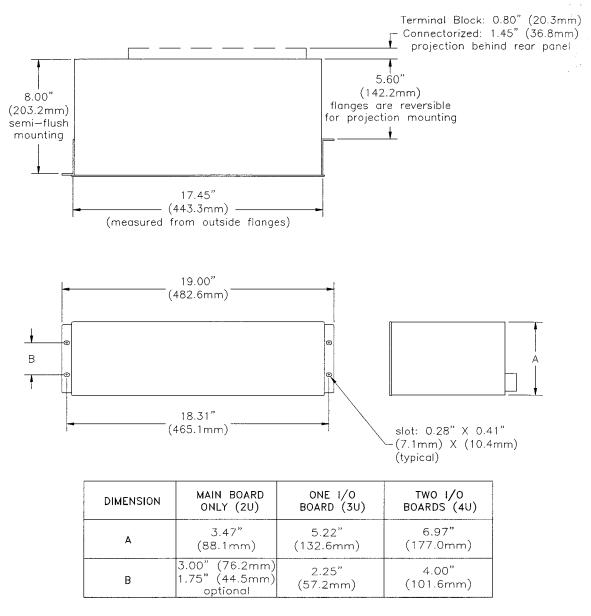

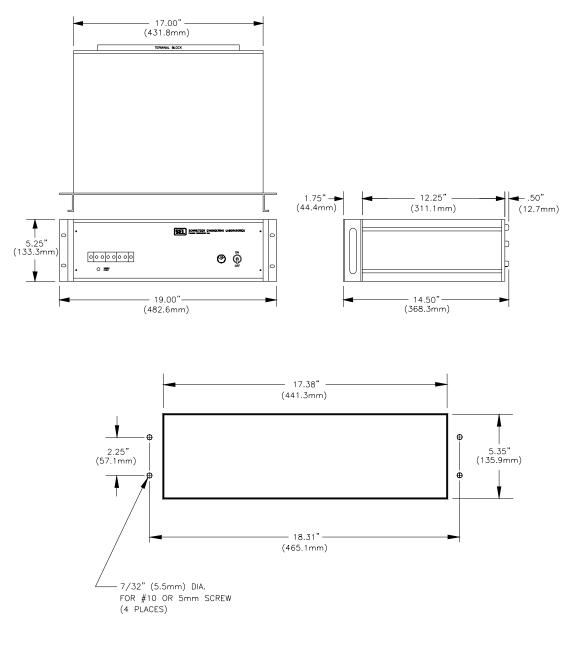

**Dimensions:** Refer to Figure 6.3 and Figure 6.5.

**Type Tests:** \*Cold: IEC 68-2-1: 1990, EN 60068-2-1: 1993, Test Ad, 16 hours at

-40°C

\*Dry Heat: IEC 68-2-2: 1974, EN 60068-2-2: 1993, Test Bd, 16 hours at

+85°C

IEC 68-2-30: 1980, Test Db, 25° to 55°C, 6 cycles, 95% Damp Heat, Cyclic:

humidity

Dielectric Strength: IEC 255-5: 1977; IEEE C37.90: 1989,

2500 Vac on analog inputs, 3100 Vdc on contact inputs,

contact outputs, and power supply

Impulse: IEC 255-5: 1977, 0.5 J, 5000 V

Vibration: IEC 255-21-1: 1988, Class 1 Shock and Bump: IEC 255-21-2: 1988, Class 1

1 MHz Burst Disturbance: IEC 255-22-1: 1988, 2.5 kV Peak, Common Mode, 1.0 kV

Peak, Differential Mode

IEC 801-2: 1991, Electrostatic Discharge:

Level 4

Radiated Radio Frequency: IEC 255-22-3: 1989, (Connectorized)

IEEE C37.90.2: 199x (draft), (Terminal Block)

10 V/m

Fast Transient Disturbance: IEC 801-4: 1988

Surge Withstand Capability: IEEE C37.90.1: 1989, 3000 V oscillatory, 5000 V fast

transient

**Note:** \* = Connectorized option only.

**Processing**

**Specifications:** 4 samples per power system cycle.

# **Fault Current Element (50FT)**

Pickup Range

5 A Model: 0.5–45.0 A 1 A Model: 0.1–9.0 A

Pickup Accuracy

Steady State:  $\pm 0.025 \text{ A} \pm 5\%$

Transient

(Scheme 6):  $\pm 5\%$

Pickup Time: Less than 0.84 cycle at 2 multiples of pickup

Dropout Time: Less than 1.1 cycles

# **MOD Current Element (50MD)**

Pickup Range

5 A Model: 0.1–45.0 A 1 A Model: 0.02–9.00 A

Pickup Accuracy

Steady State:  $\pm 0.025 \text{ A} \pm 5\%$

Pickup Time: Less than 1.1 cycles at 2 multiples of pickup

Dropout Time: Less than 1.55 cycles

# **Load/Line-Charging Current Element (50LD)**

Pickup Range

5 A Model: 0.10–45.00 A 1 A Model: 0.02–9.00 A

Pickup Accuracy

Steady State:  $\pm 0.025 \text{ A} \pm 5\%$

Pickup Time: Less than 1.1 cycles at 2 multiples of pickup

Dropout Time: Less than 1.55 cycles

#### Flashover Voltage Element (59FO)

Pickup Range: 1.0–67.0 V

Pickup Accuracy

Steady State:  $\pm 0.09 \text{ V} \pm 5\%$

Pickup Time: Less than 1.35 cycle

Dropout Time: Less than 1.55 cycles

# Negative-Sequence Overvoltage Element (47Q)

Pickup Range: 2.0-170.0 VPickup Accuracy:  $\pm 0.27 \text{ V} \pm 15\%$

Pickup Time: Less than 1.35 cycles

Dropout Time: Less than 1.55 cycles

# Flashover Voltage Element (59H)

Pickup: Fixed at 67.0 V

Pickup Accuracy: ±3.5 V

Pickup Time: Less than 1.35 cycles

Dropout Time: Less than 1.55 cycles

# **Voltage Across Closed Breaker Element (Vwarn)**

Pickup Range: 0.5–7.5 V Pickup Accuracy: ±0.09 V ±5%

Pickup Time: Less than 3 seconds

## **Current Unbalance Element (87UB)**

87UB Phase Current Unbalance Element